MCF51QE128 MCU Series Reference Manual, Rev. 3

98 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 5 Resets, Interrupts, and General System Control

Refer to Chapter 4, “Memory”, for the absolute address assignments for all registers. This section refers

to registers and control bits only by their names. A Freescale-provided equate or header file is used to

translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1 and SPMSC2 registers are related to modes of operation. Although brief

descriptions of these bits are provided here, the related functions are discussed in greater detail in

Chapter 3, “Modes of Operation”.

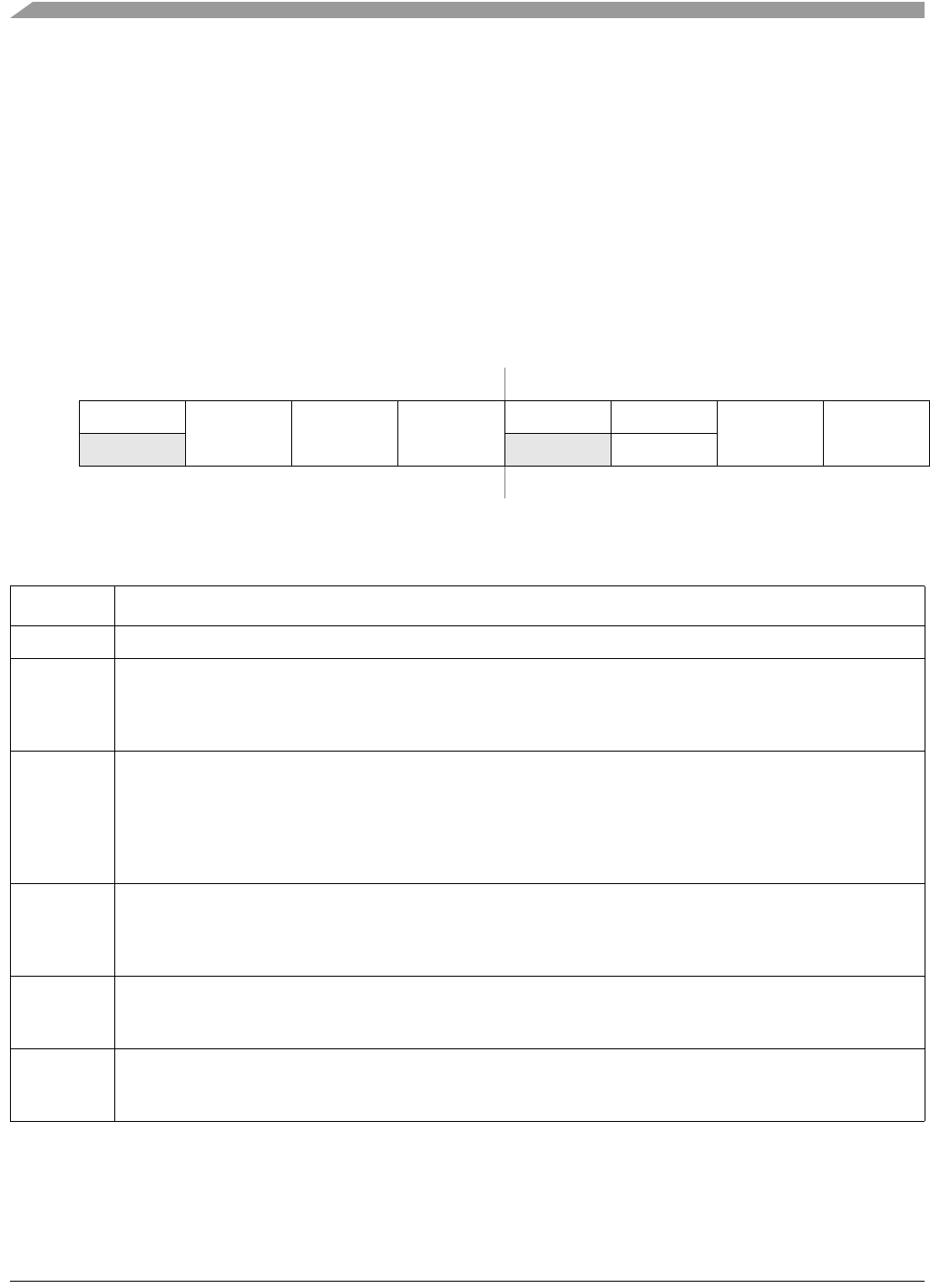

5.7.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes status and control bits which are used to configure the IRQ function,

report status, and acknowledge IRQ events.

76543210

R0

IRQPDD IRQEDG IRQPE

IRQF 0

IRQIE IRQMOD

W IRQACK

Reset00000000

Figure 5-1. Interrupt Request Status and Control Register (IRQSC)

Table 5-2. IRQSC Register Field Descriptions

Field Description

7 Reserved, should be cleared.

6

IRQPDD

Interrupt Request (IRQ) Pull Device Disable. This read/write control bit is used to disable the internal

pull-up/pull-down device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.

0 IRQ pull device enabled if IRQPE = 1.

1 IRQ pull device disabled if IRQPE = 1.

5

IRQEDG

Interrupt Request (IRQ) Edge Select. This read/write control bit selects the polarity of edges or levels on the IRQ

pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to edges and

levels or only edges. When IRQEDG is set and the internal pull device is enabled, the pull-up device is

reconfigured as an optional pull-down device.

0 IRQ is falling edge or falling edge/low-level sensitive.

1 IRQ is rising edge or rising edge/high-level sensitive.

4

IRQPE

IRQ Pin Enable. This read/write control bit enables the IRQ pin function. When this bit is set, the IRQ pin can be

used as an external interrupt request.

0 IRQ pin function is disabled.

1 IRQ pin function is enabled.

3

IRQF

IRQ Flag. This read-only status bit indicates when an interrupt request event has occurred.

0 No IRQ request.

1 IRQ event detected.

2

IRQACK

IRQ Acknowledge. This write-only bit acknowledges interrupt request events (write 1 to clear IRQF). Writing 0

has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF

cannot be cleared while the IRQ pin remains at its asserted level.