Timer/PWM Module (S08TPMV3)

MCF51QE128 MCU Series Reference Manual, Rev. 3

344 Freescale Semiconductor

Get the latest version from freescale.com

The latching mechanism may be manually reset by writing to the TPMxSC address (whether BDM is

active or not).

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxSC) so the

buffer latches remain in the state they were in when the BDM became active, even if one or both halves of

the modulo register are written while BDM is active. Any write to the modulo registers bypasses the buffer

latches and directly writes to the modulo register while BDM is active.

Reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first

counter overflow occurs.

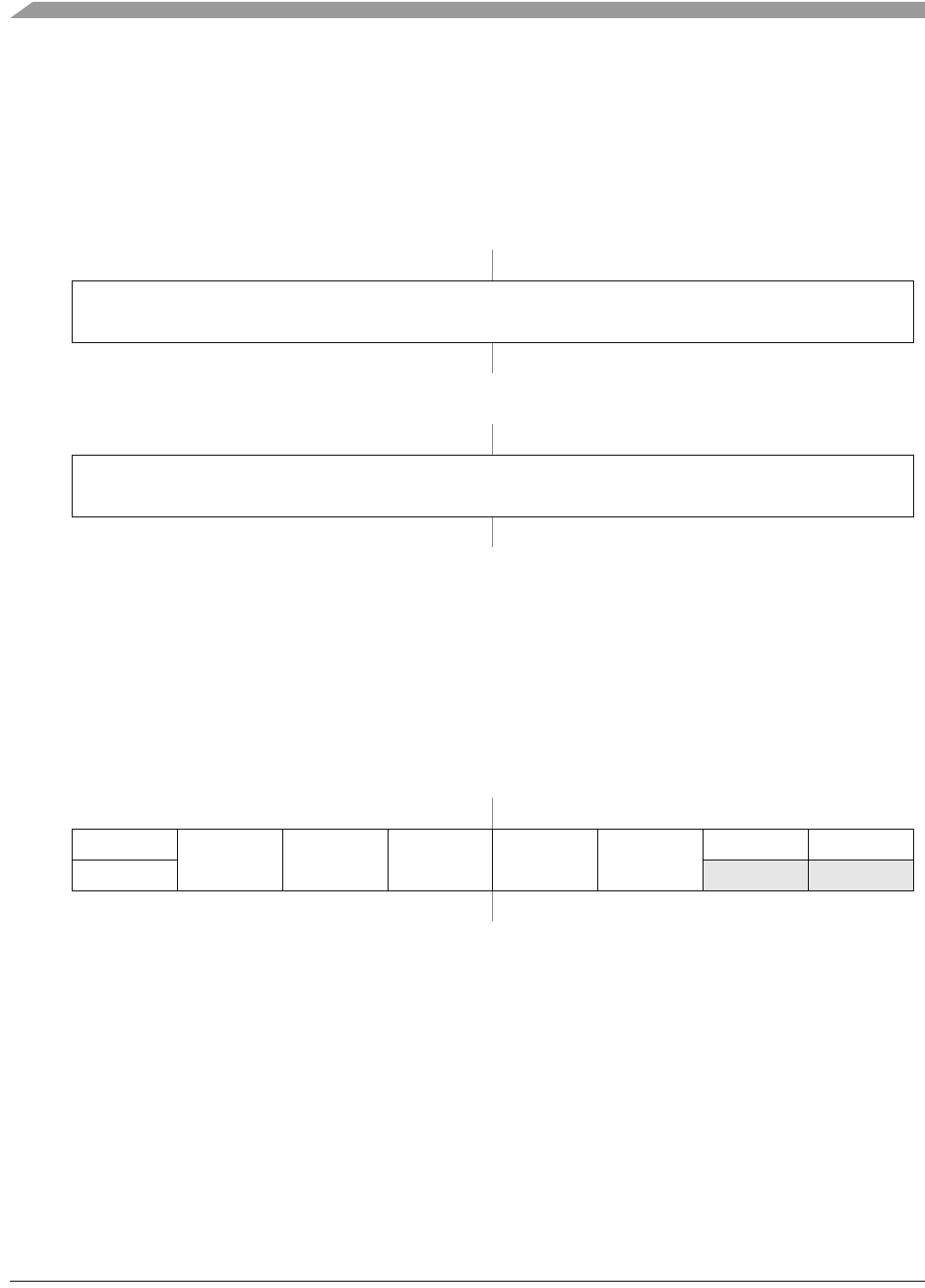

17.3.4 TPM Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel-interrupt-status flag and control bits that configure the interrupt enable,

channel configuration, and pin function.

76543210

R

TPMxMOD[15:8]

W

Reset00000000

Figure 17-10. TPM Counter Modulo Register High (TPMxMODH)

76543210

R

TPMxMOD[7:0]

W

Reset00000000

Figure 17-11. TPM Counter Modulo Register Low (TPMxMODL)

76543210

RCHnF

CHnIE MSnB MSnA ELSnB ELSnA

00

W0

Reset00000000

Figure 17-12. TPM Channel n Status and Control Register (TPMxCnSC)