ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

154 Freescale Semiconductor

7.3.2 Exception Processing Overview

Exception processing for ColdFire processors is streamlined for performance. The ColdFire processors

differ from the M68000 family because they include:

• A simplified exception vector table

• Reduced relocation capabilities using the vector-base register

• A single exception stack frame format

• Use of separate system stack pointers for user and supervisor modes.

All ColdFire processors use an instruction restart exception model. Exception processing includes all

actions from fault condition detection to the initiation of fetch for first handler instruction. Exception

processing is comprised of four major steps:

1. The processor makes an internal copy of the SR and then enters supervisor mode by setting the S

bit and disabling trace mode by clearing the T bit. The interrupt exception also forces the M bit to

be cleared and the interrupt priority mask to set to current interrupt request level.

2. The processor determines the exception vector number. For all faults except interrupts, the

processor performs this calculation based on exception type. For interrupts, the processor performs

an interrupt-acknowledge (IACK) bus cycle to obtain the vector number from the interrupt

controller if CPUCR[IAE] is set. The IACK cycle is mapped to special locations within the

interrupt controller’s address space with the interrupt level encoded in the address. If

CPUCR[IAE] is cleared, the processor uses the vector number supplied by the interrupt controller

at the time the request was signaled for improved performance.

Move from USP User Stack Pointer → Destination register

Move to USP Source register → User Stack Pointer

MVS.{B,W} Sign-extends source operand and moves it to destination register.

MVZ.{B,W} Zero-fills source operand and moves it to destination register.

SATS.L Performs saturation operation for signed arithmetic and updates destination register,

depending on CCR[V] and bit 31 of the register.

TAS.B Performs indivisible read-modify-write cycle to test and set addressed memory byte.

Bcc.L Branch conditionally, longword

BSR.L Branch to sub-routine, longword

CMP.{B,W} Compare, byte and word

CMPA.W Compare address, word

CMPI.{B,W} Compare immediate, byte and word

MOVEI Move immediate, byte and word to memory using Ax with displacement

STLDSR Pushes the contents of the status register onto the stack and then reloads the status register

with the immediate data value.

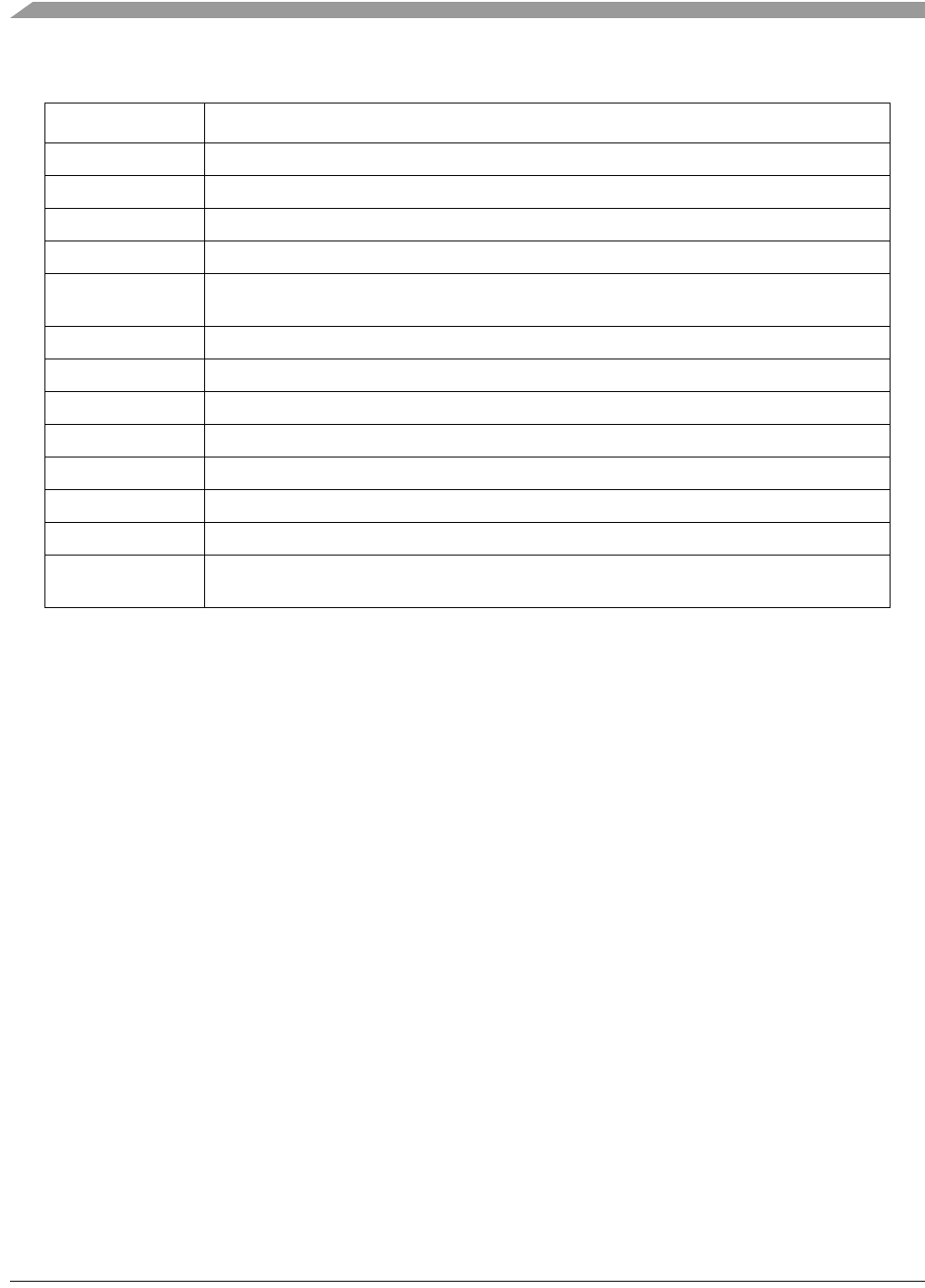

Table 7-5. Instruction Enhancements over Revision ISA_A (continued)

Instruction Description