Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

372 Freescale Semiconductor

Get the latest version from freescale.com

18.3.6 Address Attribute Trigger Register (AATR)

AATR defines address attributes and a mask to be matched in the trigger. The register value is compared

with address attribute signals from the processor’s high-speed local bus, as defined by the setting of the

trigger definition register (TDR). AATR is accessible in supervisor mode as debug control register 0x06

using the WDEBUG instruction and through the BDM port using the WRITE_DREG command.

DRc: 0x05 (BAAR) Access: Supervisor write-only

BDM write-only

313029282726252423222120191817161514131211109876543210

R

W000000000000000000000000R SZ TT TM

Reset00000000000000000000000000000101

Figure 18-7. BDM Address Attribute Register (BAAR)

Table 18-12. BAAR Field Descriptions

Field Description

31–8 Reserved for future use by the debug module, must be cleared.

7

R

Read/Write.

0Write

1Read

6–5

SZ

Size.

00 Longword

01 Byte

10 Word

11 Reserved

4–3

TT

Transfer type. See the TT definition in the AATR description, Section 18.3.6, “Address Attribute Trigger Register

(AATR)”.

2–0

TM

Transfer modifier. See the TM definition in the AATR description, Section 18.3.6, “Address Attribute Trigger Register

(AATR)”.

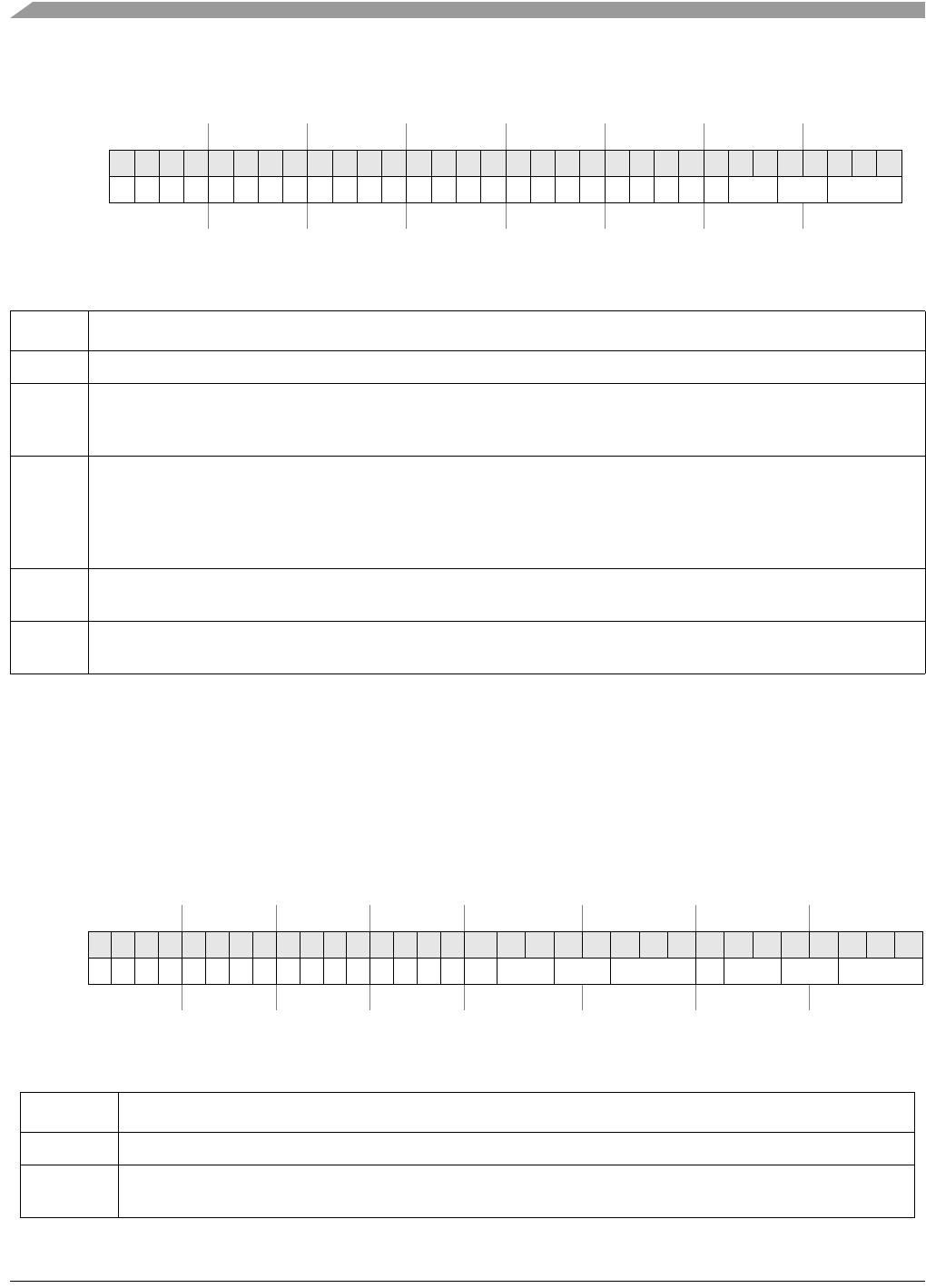

DRc: 0x06 (AATR) Access: Supervisor write-only

BDM write-only

313029282726252423222120191817161514131211109876543210

R

W0000000000000000RMSZM TTM TMM R SZ TT TM

Reset0000000000000000 0 000000000000101

Figure 18-8. Address Attribute Trigger Register (AATR)

Table 18-13. AATR Field Descriptions

Field Description

31–16 Reserved, must be cleared.

15

RM

Read/write mask. Masks the R bit in address comparisons.