MCF51QE128 MCU Series Reference Manual, Rev. 3

304 Freescale Semiconductor

Get the latest version from freescale.com

framing errors are inhibited and the break detection threshold changes from 10 bits to 11 bits, preventing

false detection of a 0x00 data character as a LIN break symbol.

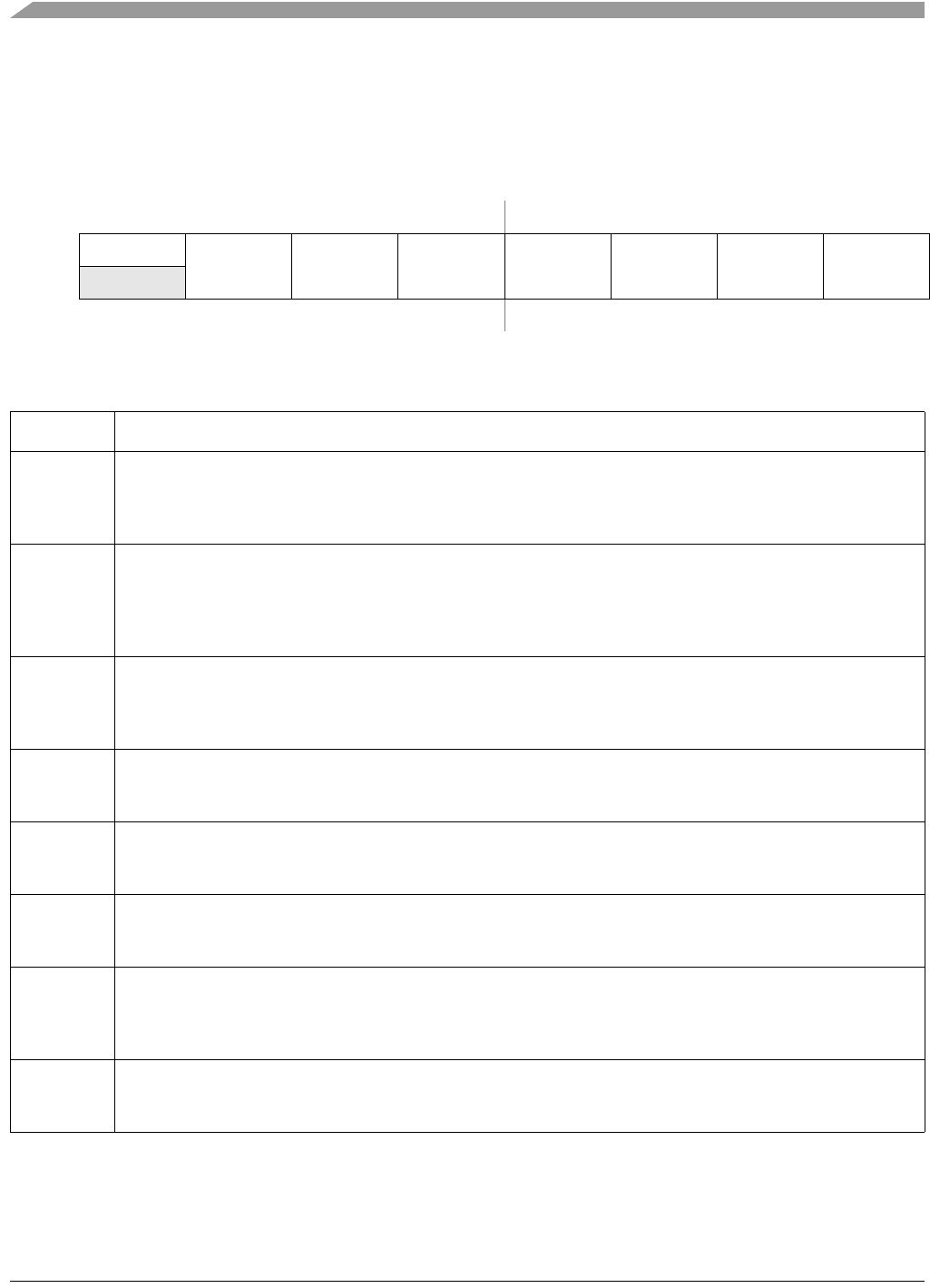

15.2.6 SCI Control Register 3 (SCIxC3)

76543210

RR8

T8 TXDIR TXINV ORIE NEIE FEIE PEIE

W

Reset00000000

Figure 15-11. SCI Control Register 3 (SCIxC3)

Table 15-7. SCIxC3 Field Descriptions

Field Description

7

R8

Ninth Data Bit for Receiver. When the SCI is configured for 9-bit data (M = 1), R8 can be thought of as a ninth

receive data bit to the left of the msb of the buffered data in the SCIxD register. When reading 9-bit data, read

R8 before reading SCIxD because reading SCIxD completes automatic flag clearing sequences which could

allow R8 and SCIxD to be overwritten with new data.

6

T8

Ninth Data Bit for Transmitter. When the SCI is configured for 9-bit data (M = 1), T8 may be thought of as a ninth

transmit data bit to the left of the msb of the data in the SCIxD register. When writing 9-bit data, the entire 9-bit

value is transferred to the SCI shift register after SCIxD is written so T8 should be written (if it needs to change

from its previous value) before SCIxD is written. If T8 does not need to change in the new value (such as when

it is used to generate mark or space parity), it need not be written each time SCIxD is written.

5

TXDIR

TxD Pin Direction in Single-Wire Mode. When the SCI is configured for single-wire half-duplex operation

(LOOPS = RSRC = 1), this bit determines the direction of data at the TxD pin.

0 TxD pin is an input in single-wire mode.

1 TxD pin is an output in single-wire mode.

4

TXINV

1

1

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

Transmit Data Inversion. Setting this bit reverses the polarity of the transmitted data output.

0 Transmit data not inverted

1 Transmit data inverted

3

ORIE

Overrun Interrupt Enable. This bit enables the overrun flag (OR) to generate hardware interrupt requests.

0 OR interrupts disabled (use polling).

1 Hardware interrupt requested when OR is set.

2

NEIE

Noise Error Interrupt Enable. This bit enables the noise flag (NF) to generate hardware interrupt requests.

0 NF interrupts disabled (use polling).

1 Hardware interrupt requested when NF is set.

1

FEIE

Framing Error Interrupt Enable. This bit enables the framing error flag (FE) to generate hardware interrupt

requests.

0 FE interrupts disabled (use polling).

1 Hardware interrupt requested when FE is set.

0

PEIE

Parity Error Interrupt Enable. This bit enables the parity error flag (PF) to generate hardware interrupt requests.

0 PF interrupts disabled (use polling).

1 Hardware interrupt requested when PF is set.