MCF51QE128 MCU Series Reference Manual, Rev. 3

68 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 4 Memory

The factory trim values are stored in the flash information row (IFR)

1

and are automatically loaded into

the ICSTRM and ICSSC registers after any reset. The oscillator trim values stored in TRIM and FTRIM

can be reprogrammed by third party programmers and must be copied into the corresponding ICS registers

(ICSTRM and ICSSC) by user code to override the factory trim.

NOTE

When the MCU is in active BDM, the trim value in the IFR is not loaded.

Instead, the ICSTRM register resets to 0x80 and ICSSC[FTRIM] resets to

zero.

Provided the key enable (KEYEN) bit is set, the 8-byte comparison key can be used to temporarily

disengage memory security. This key mechanism can be accessed only through user code running in secure

memory (A security key cannot be entered directly through background debug commands). This security

key can be disabled completely by clearing the KEYEN bit. If the security key is disabled, the only way

0x(00)00_0408

Reserved

0x(00)00_040C

Reserved NVPROT Reserved NVOPT

1

MSB = most significant byte

2

LSB = least significant byte

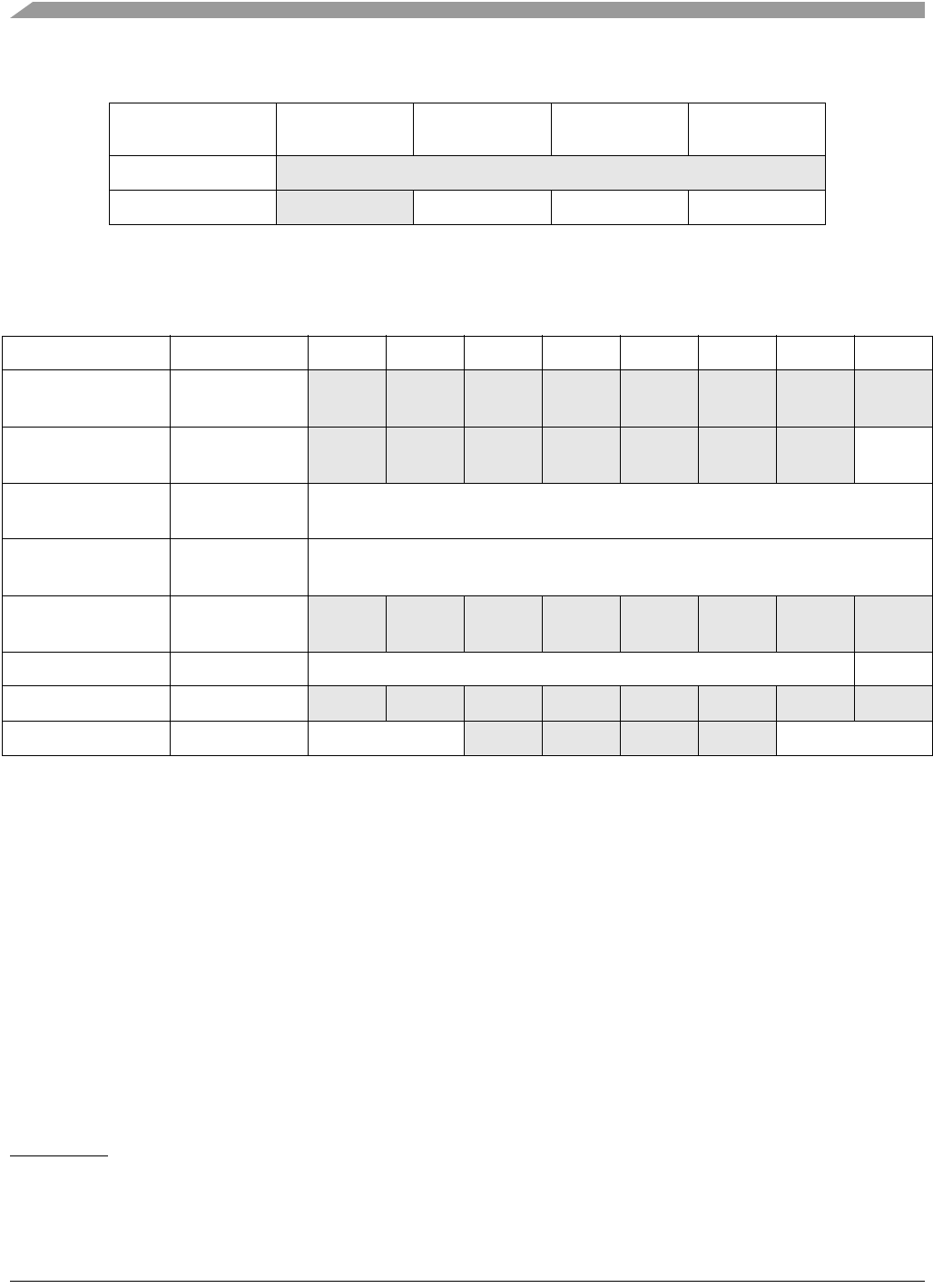

Table 4-5. Reserved Flash Memory Addresses

Address Register76543210

0x(00)00_03FC–

0x(00)00_03FD

Reserved

— — — — — — — —

0x(00)00_03FE

Storage of

FTRIM

0 0 0 0 0 0 0 FTRIM

0x(00)00_03FF

Storage of

ICSTRM

TRIM

0x(00)00_0400–

0x(00)00_0407

8-Byte Backdoor Comparison Key

0x(00)00_0408–

0x(00)00_040C

Reserved

— — — — — — — —

0x(00)00_040D NVPROT

FPS FPOPEN

0x(00)00_040E

Reserved — — — — — — — —

0x(00)00_040F

NVOPT KEYEN 0 0 0 0 SEC

1. IFR — Nonvolatile information memory that can only be accessed during production test. During production test, system

initialization, configuration, and test information is stored in the IFR. This information cannot be read or modified in normal

user or background debug modes.

Table 4-4. Reserved Flash Memory Addresses

Address

MSB

1

(0x0) (0x1) (0x2)

LSB

2

(0x3)