Internal Clock Source (S08ICSV3)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 253

Get the latest version from freescale.com

r

1

OSCINIT

OSC Initialization. If EREFS is set and the external reference clock is selected by ERCLKEN or by the ICS being

in FEE, FBE, or FBELP mode, this bit is set after the initialization cycles of the external oscillator clock have

completed. This bit is only cleared when either ERCLKEN or EREFS are cleared.

0

FTRIM

ICS Fine Trim. The FTRIM bit controls the smallest adjustment of the internal reference clock frequency. Setting

FTRIM increases the period and clearing FTRIM decreases the period by the smallest amount possible.

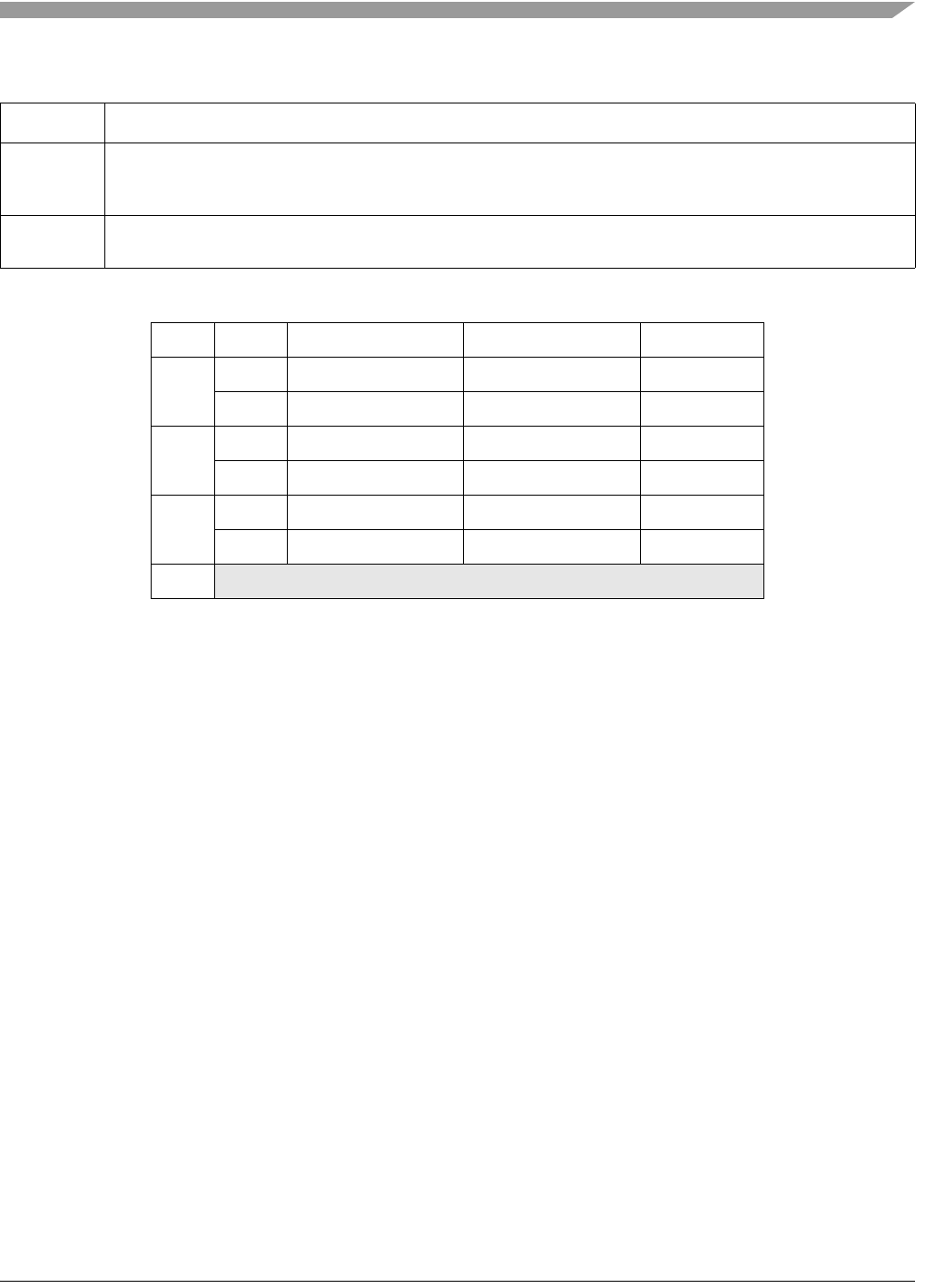

Table 12-7. DCO Frequency Range

1

1

The resulting bus clock frequency should not exceed the maximum specified bus

clock frequency of the device.

DRS DMX32 Reference range FLL factor DCO range

00

0

31.25 – 39.0625 kHz

512 16 – 20 MHz

1

32.768 kHz

608 19.92 MHz

01

0

31.25 – 39.0625 kHz

1024 32 – 40 MHz

1

32.768 kHz

1216 39.85 MHz

10

0

31.25 – 39.0625 kHz

1536 48 – 60 MHz

1

32.768 kHz

1824 59.77 MHz

11

Reserved

Table 12-6. ICSSC Field Descriptions (continued)

Field Description