MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 185

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

8.3.3 Interrupt Request Level and Priority Assignments

This section provides two views of the interrupt request assignment: a two-dimensional view of levels and

priorities within the level (Table 8-11) and a tabular representation based on request priority (Table 8-12).

The CF1_INTC module implements a sparsely-populated 7 × 9 matrix of levels (7) and priorities within

each level (9). In this representation, the leftmost top cell (level 7, priority 7) is the highest interrupt request

while the rightmost lowest cell (level 1, priority 0) is the lowest interrupt request. The following legend is

used for this table:

NOTE

For remapped and forced interrupts, the interrupt source number entry

indicates the register or register field that enables the corresponding

interrupt.

Table 8-9. INTC_SWIACK, INTC_LVLnIACK Field Descriptions

Field Description

7 Reserved, must be cleared.

6–0

VECN

Vector number. Indicates the appropriate vector number.

For the SWIACK register, it is the highest-level, highest-priority request currently being asserted in the CF1_INTC

module. If there are no pending requests, VECN is zero.

For the LVLnIACK register, it is the highest priority request within the specified level-n. If there are no pending

requests within the level, VECN is 0x18 (24) to signal a spurious interrupt.

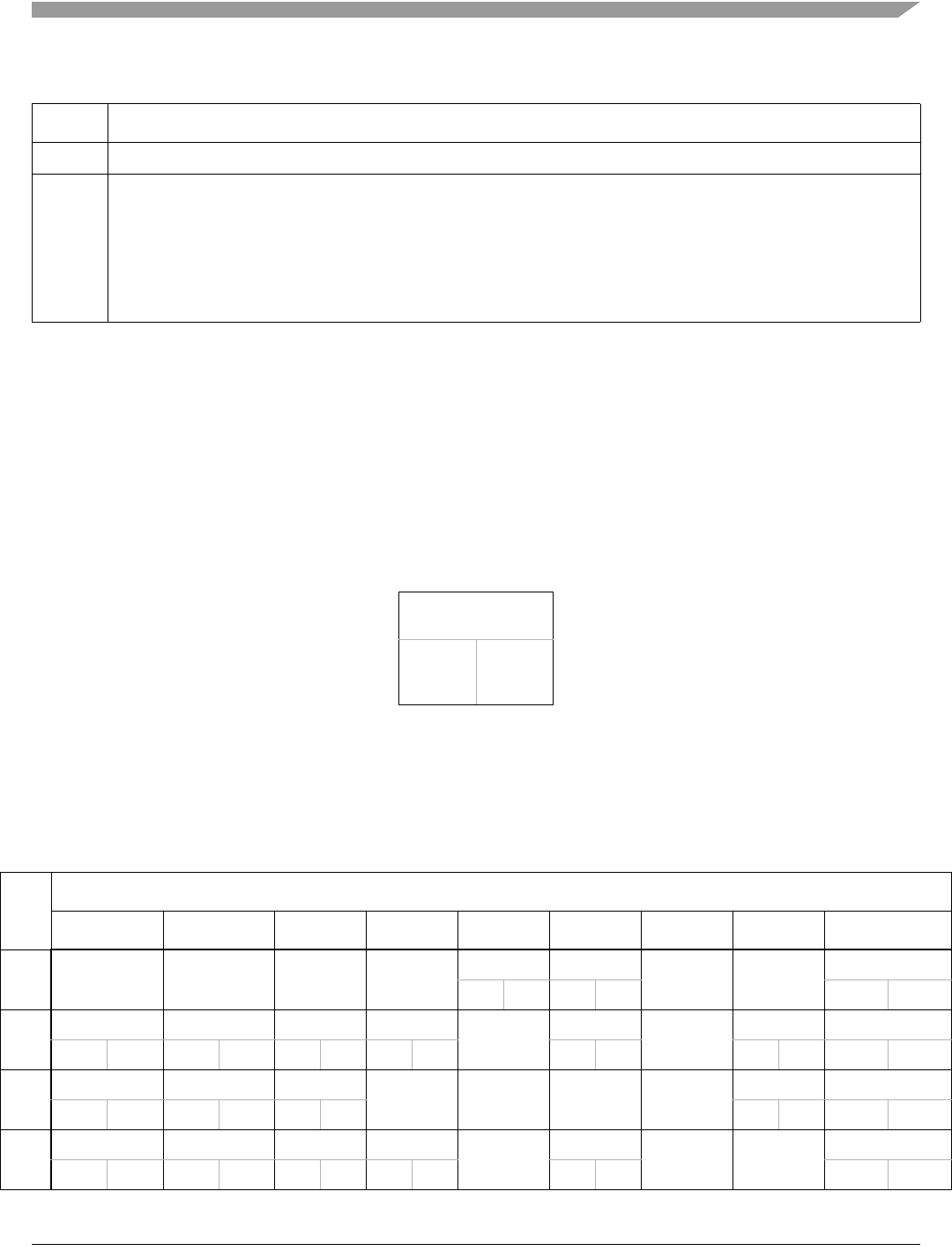

Table 8-10. Legend for Table 8-11

Interrupt Request

Source

Interrupt

Source

Number

Vector

Number

Table 8-11. V1 ColdFire [Level][Priority within Level] Matrix Interrupt Assignments

Level

Priority within Level

7 6 54Midpoint321 0

7

————

IRQ_pin Low_voltage

——

force_lvl7

064165 FRC[32]96

6

remapped remapped TPM1_ch0 TPM1_ch1

—

TPM1_ch2

—

TPM1_ovfl force_lvl6

PL6P7 * PL6P6 * 2 66 3 67 4 68 5 69 FRC[33] 97

5

TPM2_ch0 TPM2_ch1 TPM2_ch12

————

TPM2_ovfl force_lvl5

6 70 7 71 8 72 9 73 FRC[34] 98

4

SPI2 SPI1 SCI1_err SCI1_rx

—

SCI1_tx

——

force_lvl4

10 74 11 75 12 76 13 77 14 78 FRC[35] 99