ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 151

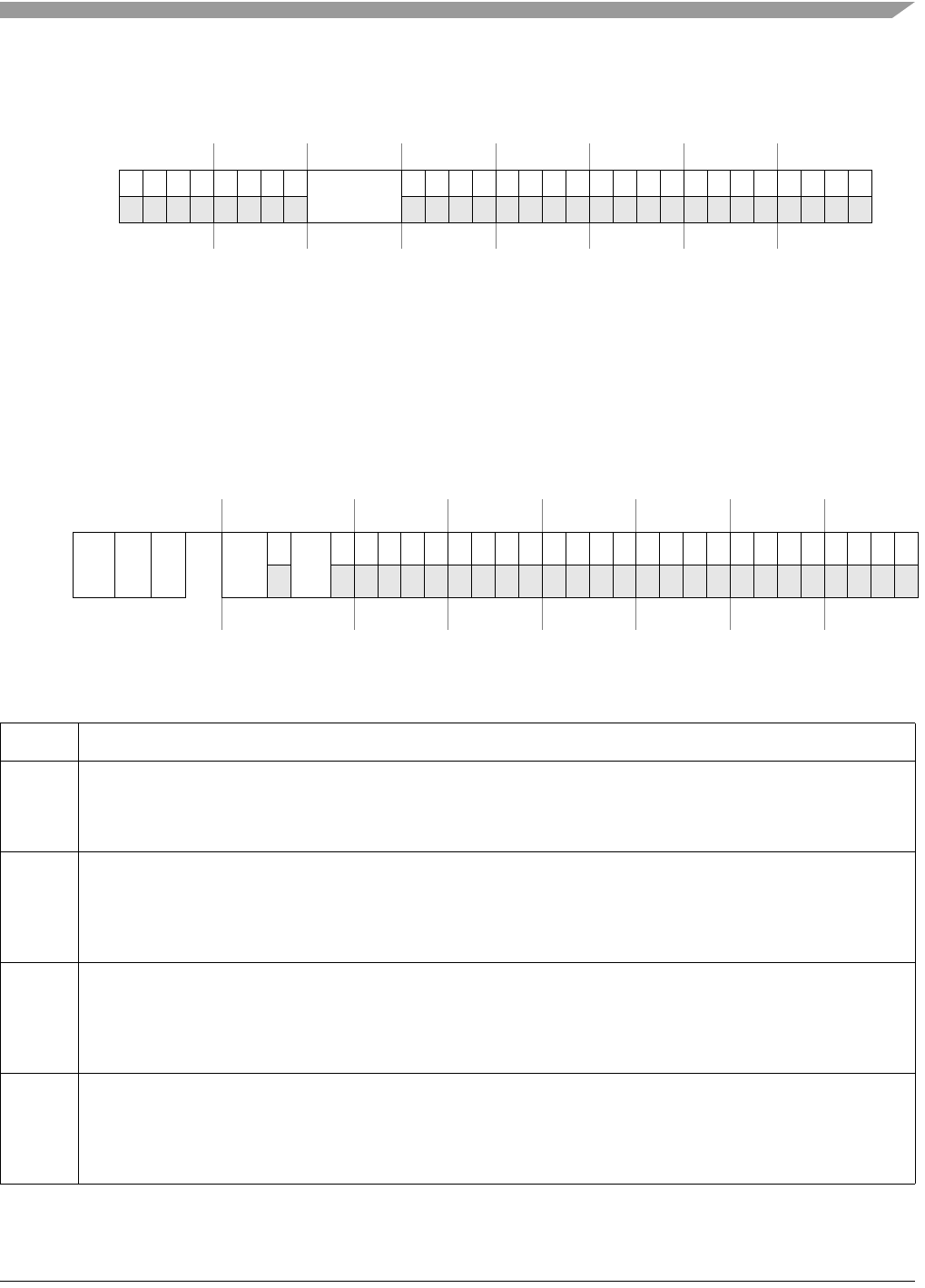

Figure 7-7. Vector Base Register (VBR)

7.2.7 CPU Configuration Register (CPUCR)

The CPUCR provides supervisor mode configurability of specific core functionality. Certain hardware

features can be enabled/disabled individually based on the state of the CPUCR.

Figure 8. CPU Configuration Register (CPUCR)

BDM: 0x801 (VBR)

Load: 0xE1 (VBR)

Store: 0xC1 (VBR)

Access: Supervisor read/write

BDM read/write

313029282726252423222120191817161514131211109876543210

R 0 0 0 0 0 000

Base

Address

0 0 0 0 0 000000000 000 0 00

W

Reset00000000000000000000000000000000

BDM: 0x802 (CPUCR)

Load: 0xE2 (CPUCR)

Store: 0xC2 (CPUCR)

Access: Supervisor read/write

BDM read/write

31 30 29 28 27 26252423222120191817161514131211109876543210

R

ARD IRD IAE IME BWD

0

FSD

0000000 0 0 0 000000000 000 0 00

W

Reset 0 0 0 0 0 0 0 0000000000000000000000000

Table 3. CPUCR Field Descriptions

Field Description

31

ARD

Address-related reset disable. Used to disable the generation of a reset event in response to a processor exception

caused by an address error, a bus error, an RTE format error, or a fault-on-fault halt condition.

0 The detection of these types of exception conditions or the fault-on-fault halt condition generate a reset event.

1 No reset is generated in response to these exception conditions.

30

IRD

Instruction-related reset disable. Used to disable the generation of a reset event in response to a processor exception

caused by the attempted execution of an illegal instruction (except for the ILLEGAL opcode), illegal line A, illegal

line F instructions, or a privilege violation.

0 The detection of these types of exception conditions generate a reset event.

1 No reset is generated in response to these exception conditions.

29

IAE

Interrupt acknowledge (IACK) enable. Forces the processor to generate an IACK read cycle from the interrupt

controller during exception processing to retrieve the vector number of the interrupt request being acknowledged. The

processor’s execution time for an interrupt exception is slightly improved when this bit is cleared.

0 The processor uses the vector number provided by the interrupt controller at the time the request is signaled.

1 IACK read cycle from the interrupt controller is generated.

28

IME

Interrupt mask enable.

Forces the processor to raise the interrupt level mask (SR[I]) to 7 during every

interrupt exception. This capability is provided to assist when porting S08 application code to ColdFire.

0 As part of an interrupt exception, the processor sets SR[I] to the level of the interrupt being serviced.

1 As part of an interrupt exception, the processor sets SR[I] to 7. This disables all level 1-6 interrupt requests but

allows recognition of the edge-sensitive level 7 requests.