Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 413

Get the latest version from freescale.com

18.4.3.2 PST Trace Buffer (PSTB)

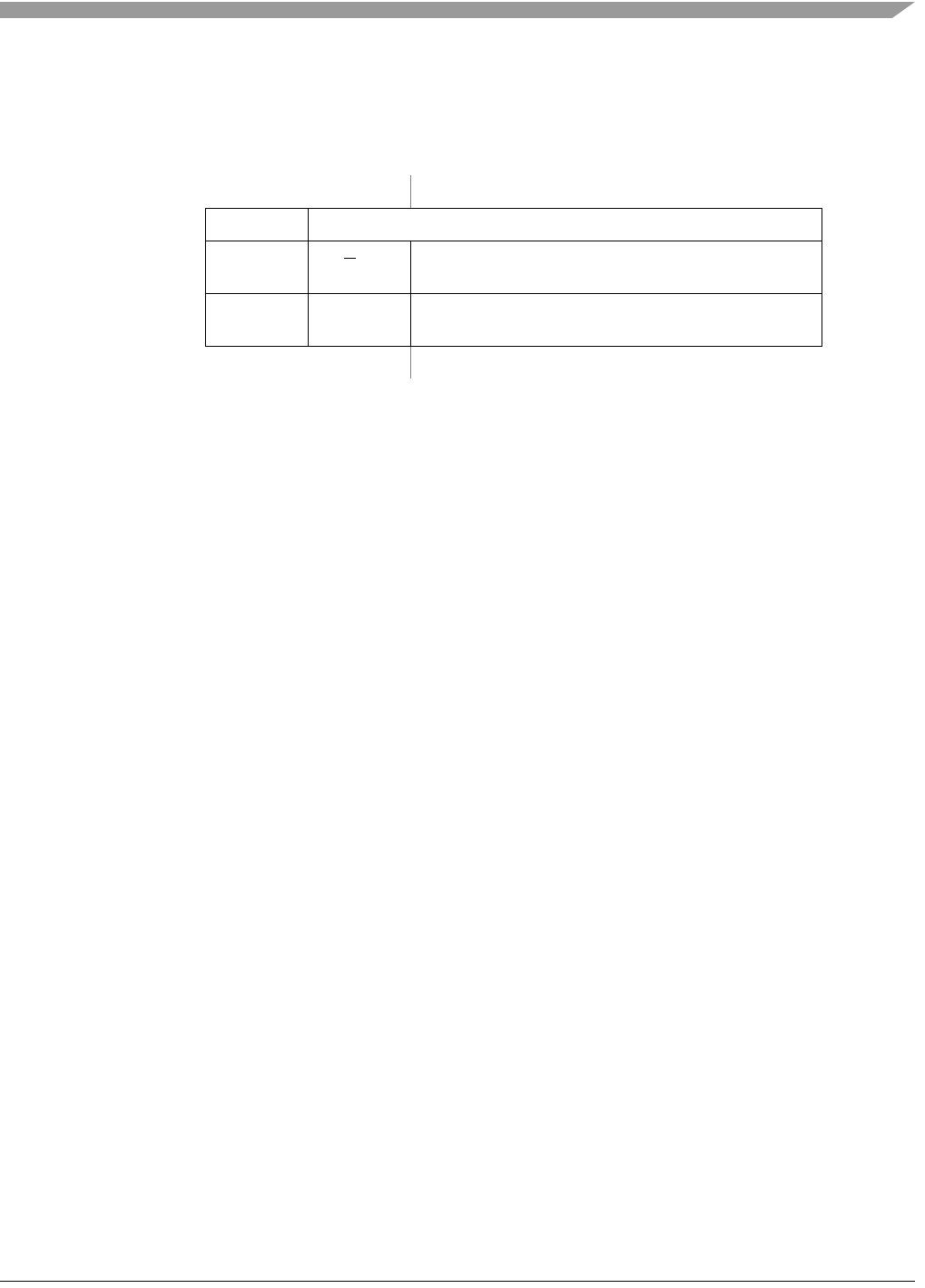

As PST and DDATA values are captured and loaded in the trace buffer, each entry is 6 bits in size so the

type of the entry can easily be determined when post-processing the PSTB. See Figure 18-24.

Figure 18-24. V1 PST/DDATA Trace Buffer Entry Format

18.4.3.3 PST/DDATA Example

In this section, an example showing the behavior of the PST/DDATA functionality is detailed. Consider

the following interrupt service routine that counts the interrupt, then negates the IRQ, and performs a

software IACK and then exits. This example is presented here because it exercises a considerable set of

the PST/DDATA capabilities.

_isr:

01074: 46fc 2700 mov.w &0x2700,%sr # disable interrupts

01078: 2f08 mov.l %a0,-(%sp) # save a0

0107a: 2f00 mov.l %d0,-(%sp) # save d0

0107c: 302f 0008 mov.w (8,%sp),%d0 # load format/vector word

01080: e488 lsr.l &2,%d0 # align vector number

01082: 0280 0000 00ff andi.l &0xff,%d0 # isolate vector number

01088: 207c 0080 1400 mov.l &int_count,%a0 # base of interrupt counters

_isr_entry1:

0108e: 52b0 0c00 addq.l &1,(0,%a0,%d0.l*4) # count the interrupt

01092: 11c0 a021 mov.b %d0,IGCR0+1.w # negate the irq

01096: 1038 a020 mov.b IGCR0.w,%d0 # force the write to complete

0109a: 4e71 nop # synchronize the pipelines

0109c: 71b8 ffe0 mvz.b SWIACK.w,%d0 # software iack: pending irq?

010a0: 0c80 0000 0041 cmpi.l %d0,&0x41 # level 7 or none pending?

010a6: 6f08 ble.b _isr_exit # yes, then exit

010a8: 52b9 0080 145c addq.l &1,swiack_count # increment the swiack count

010ae: 60de bra.b _isr_entry1 # continue at entry1

_isr_exit:

010b0: 201f mov.l (%sp)+,%d0 # restore d0

010b2: 205f mov.l (%sp)+,%a0 # restore a0

010b4: 4e73 rte # exit

This ISR executes mostly as straight-line code: there is a single conditional branch @ PC = 0x10A6, which

is taken in this example. The following description includes the PST and DDATA values generated as this

code snippet executes. In this example, the CSR setting enables the display of 2-byte branch addresses.

Peripheral bus read and write operands are being traced. The sequence begins with an interrupt exception:

interrupt exception occurs @ pc = 5432 while in user mode

543210

PSTB[PST] 0 PST[4:0]

Data

PSTB[DDATA]

1R

/W Data[3:0]

Address

PSTB[DDATA]

1 0 Address[3:0]

Reset:——————