MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 179

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

The programming model follows the definition from previous ColdFire interrupt controllers. This

compatibility accounts for the various memory holes in this module’s memory map.

8.3.1 Memory Map

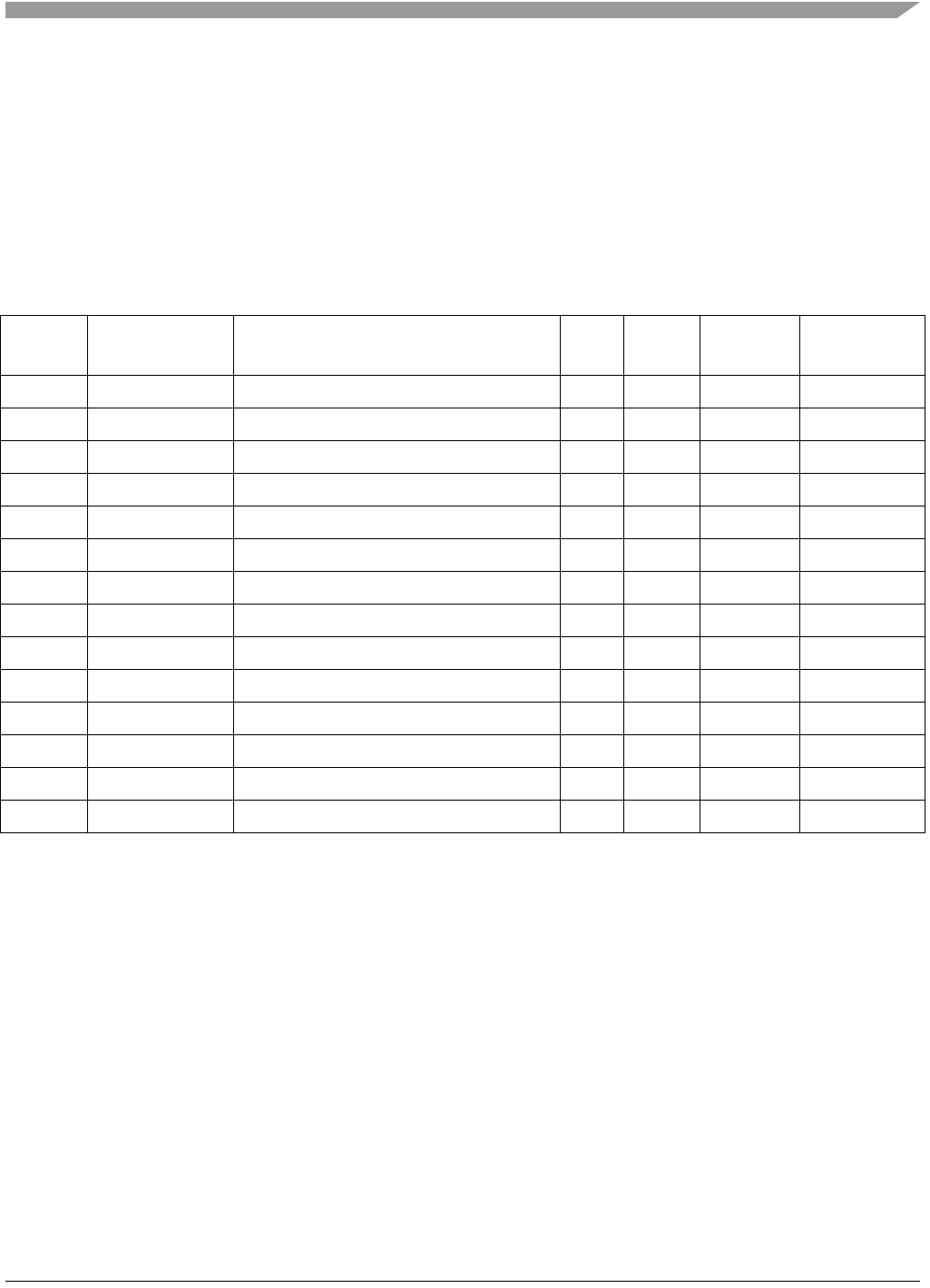

The CF1_INTC module is based at address 0x(FF)FF_FFC0 (referred to as CF1_INTC_BASE throughout

the chapter) and occupies the upper 64 bytes of the peripheral space. The module memory map is shown

in Table 8-3.

8.3.2 Register Descriptions

The following sections detail the individual registers within the CF1_INTC’s programming model.

8.3.2.1 INTC Force Interrupt Register (INTC_FRC)

The INTC_FRC register allows software to generate a unique interrupt for each possible level at the lowest

priority within the level for functional or debug purposes. These interrupts may be self-scheduled by

setting one or more of the bits in the INTC_FRC register. In some cases, the handling of a normal interrupt

request may cause critical processing by the service routine along with the scheduling (using the

INTC_FRC register) of a lower priority level interrupt request to be processed at a later time for

less-critical task handling.

The INTC_FRC register may be modified directly using a read-modify-write sequence or through a simple

write operation using the set/clear force interrupt registers (INTC_SFRC, INTC_CFRC).

Table 8-3. CF1_INTC Memory Map

Offset

Address

Register Name Register Description

Width

(bits)

Access

Reset

Value

Section/

Page

0x13 INTC_FRC CF1_INTC Force Interrupt Register 8 R/W 0x00 8.3.2.1/8-179

0x18 INTC_PL6P7 CF1_INTC Programmable Level 6, Priority 7 8 R/W 0x00 8.3.2.2/8-180

0x19 INTC_PL6P6 CF1_INTC Programmable Level 6, Priority 6 8 R/W 0x00 8.3.2.2/8-180

0x1B INTC_WCR CF1_INTC Wake-up Control Register 8 R/W 0x00 8.3.2.3/8-181

0x1E INTC_SFRC CF1_INTC Set Interrupt Force Register 8 Write — 8.3.2.4/8-182

0x1F INTC_CFRC CF1_INTC Clear Interrupt Force Register 8 Write — 8.3.2.5/8-183

0x20 INTC_SWIACK CF1_INTC Software Interrupt Acknowledge 8 Read 0x00 8.3.2.6/8-184

0x24 INTC_LVL1IACK CF1_INTC Level 1 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x28 INTC_LVL2IACK CF1_INTC Level 2 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x2C INTC_LVL3IACK CF1_INTC Level 3 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x30 INTC_LVL4IACK CF1_INTC Level 4 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x34 INTC_LVL15ACK CF1_INTC Level 5 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x38 INTC_LVL6IACK CF1_INTC Level 6 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184

0x3C INTC_LVL7IACK CF1_INTC Level 7 Interrupt Acknowledge 8 Read 0x18 8.3.2.6/8-184