Timer/PWM Module (S08TPMV3)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 343

Get the latest version from freescale.com

little-endian order that makes this more friendly to various compiler implementations. The coherency

mechanism is automatically restarted by an MCU reset or any write to the timer status/control register

(TPMxSC).

Reset clears the TPM counter registers. Writing any value to TPMxCNTH or TPMxCNTL also clears the

TPM counter (TPMxCNTH:TPMxCNTL) and resets the coherency mechanism, regardless of the data

involved in the write.

When BDM is active, the timer counter is frozen (this is the value read by user). The coherency mechanism

is frozen so the buffer latches remain in the state they were in when the BDM became active, even if one

or both counter halves are read while BDM is active. This assures that if the user was in the middle of

reading a 16-bit register when BDM became active, it reads the appropriate value from the other half of

the 16-bit value after returning to normal execution.

In BDM mode, writing any value to TPMxSC, TPMxCNTH, or TPMxCNTL registers resets the read

coherency mechanism of the TPMxCNTH:L registers, regardless of the data involved in the write.

17.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM

counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock, and

the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits the TOF bit and

overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000

which results in a free running timer counter (modulo disabled).

Writing to either byte (TPMxMODH or TPMxMODL) latches the value into a buffer and the registers are

updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

• If CLKSB and CLKSA are cleared, the registers are updated when the second byte is written

• If CLKSB and CLKSA are not cleared, the registers are updated after both bytes were written, and

the TPM counter changes from (TPMxMODH:TPMxMODL - 1) to

(TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made

when the TPM counter changes from 0xFFFE to 0xFFFF

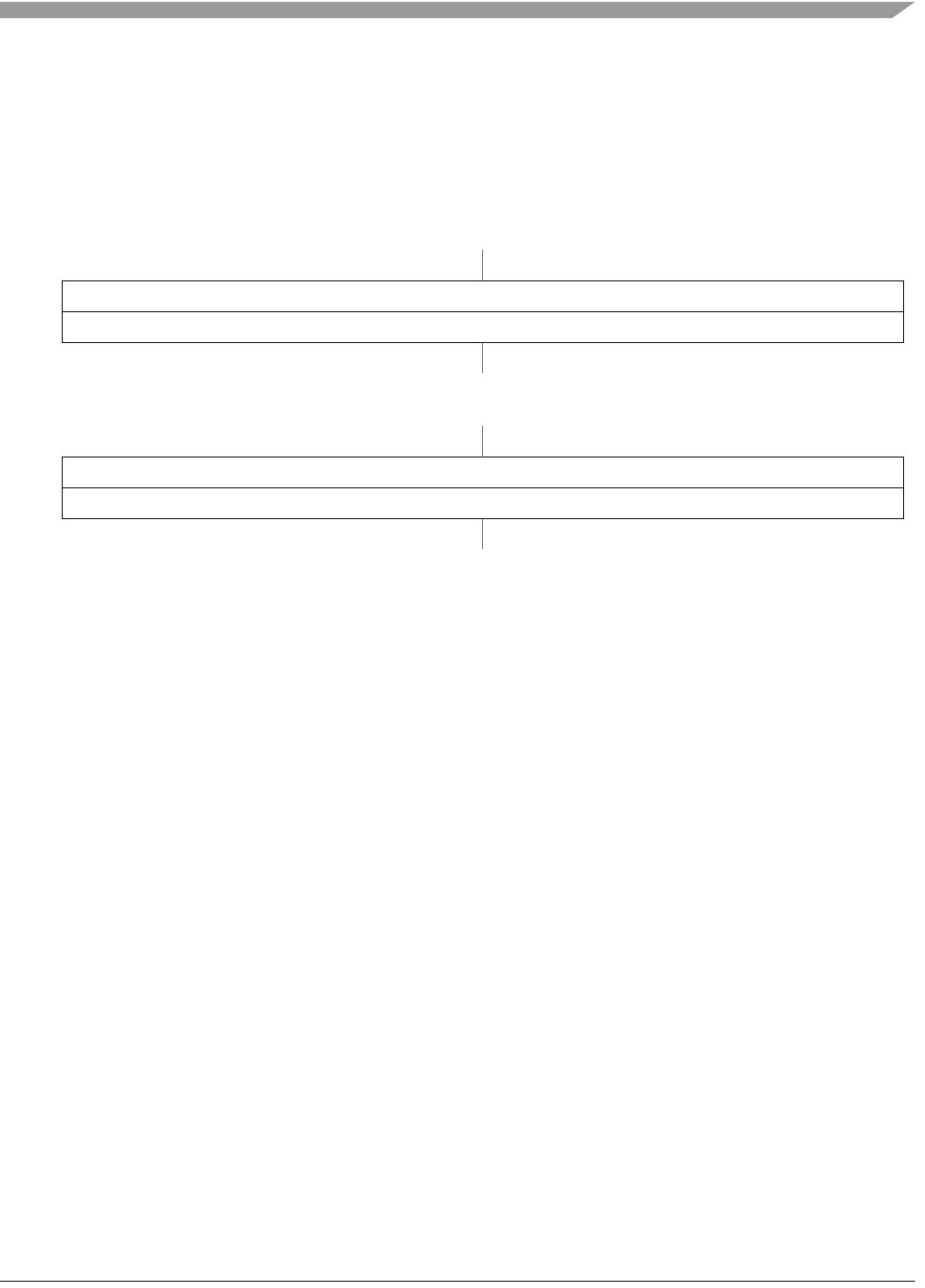

76543210

R TPMxCNT[15:8]

W Any write to TPMxCNTH clears the 16-bit counter

Reset00000000

Figure 17-8. TPM Counter Register High (TPMxCNTH)

76543210

R TPMxCNT[7:0]

W Any write to TPMxCNTL clears the 16-bit counter

Reset00000000

Figure 17-9. TPM Counter Register Low (TPMxCNTL)