MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 323

Get the latest version from freescale.com

16.4.3 SPI Baud Rate Register (SPIxBR)

This register sets the prescaler and bit rate divisor for an SPI master. This register may be read or written

at any time.

76543210

R000

MODFEN BIDIROE

0

SPISWAI SPC0

W

Reset00000000

Figure 16-6. SPI Control Register 2 (SPIxC2)

Table 16-3. SPIxC2 Register Field Descriptions

Field Description

7–5 Reserved, should be cleared.

4

MODFEN

Master Mode-Fault Function Enable. When the SPI is configured for slave mode, this bit has no meaning or effect.

(The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to

Ta bl e 1 6- 2 for more details).

0 Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI

1 Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output

3

BIDIROE

Bidirectional Mode Output Enable. When bidirectional mode is enabled by setting SPC0, BIDIROE determines

whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin. Depending on whether the

SPI is configured as a master or a slave, it uses the MOSI (MOMI) or MISO (SISO) pin, respectively, as the single

SPI data I/O pin. When SPC0 is cleared, BIDIROE has no meaning or effect.

0 Output driver disabled so SPI data I/O pin acts as an input

1 SPI I/O pin enabled as an output

2 Reserved, should be cleared.

1

SPISWAI

SPI Stop in Wait Mode

0 SPI clocks continue to operate in wait mode

1 SPI clocks stop when the MCU enters wait mode

0

SPC0

SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR is cleared (slave mode), the

SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR is set (master mode), the SPI uses

the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 is set 1, BIDIROE enables or disables the

output driver for the single bidirectional SPI I/O pin.

0 SPI uses separate pins for data input and data output

1 SPI configured for single-wire bidirectional operation

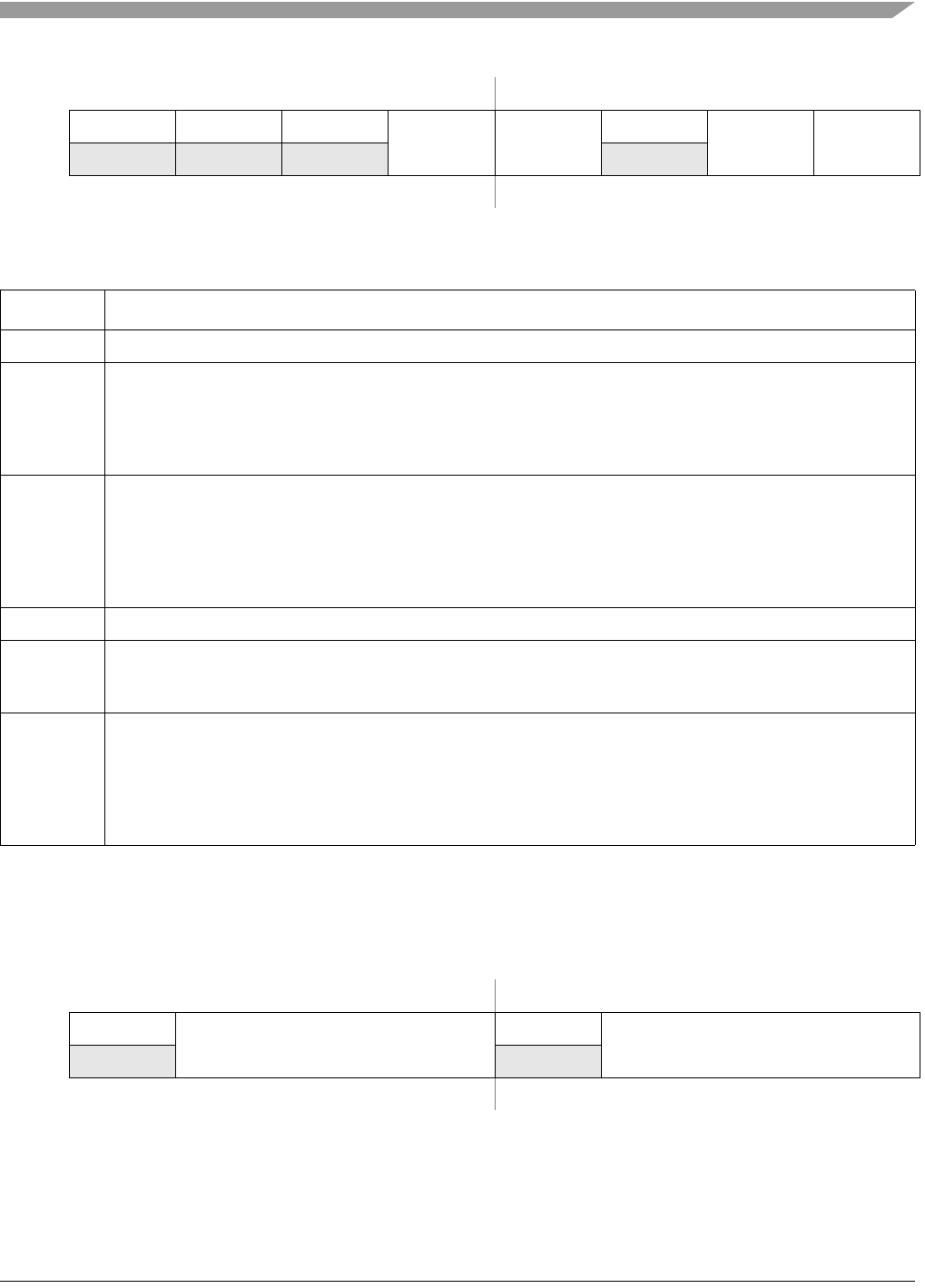

76543210

R0

SPPR

0

SPR

W

Reset00000000

Figure 16-7. SPI Baud Rate Register (SPIxBR)