MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 173

Get the latest version from freescale.com

Chapter 8

Interrupt Controller (CF1_INTC)

8.1 Introduction

This interrupt controller (CF1_INTC) is intended for use in low-cost microcontroller designs using the

Version 1 (V1) ColdFire processor core. In keeping with the general philosophy for devices based on this

low-end 32-bit processor, the interrupt controller generally supports less programmability compared to

similar modules in other ColdFire microcontrollers and embedded microprocessors. However, CF1_INTC

provides the required functionality with a minimal silicon cost.

These requirements guide the CF1_INTC module definition to support Freescale’s Controller Continuum:

• The priorities of the interrupt requests between comparable HCS08 and V1 ColdFire devices are

identical.

• Supports a mode of operation (via software convention with hardware assists) equivalent to the

S08’s interrupt processing with only one level of nesting.

• Leverages the current ColdFire interrupt controller programming model and functionality, but with

a minimal hardware implementation and cost.

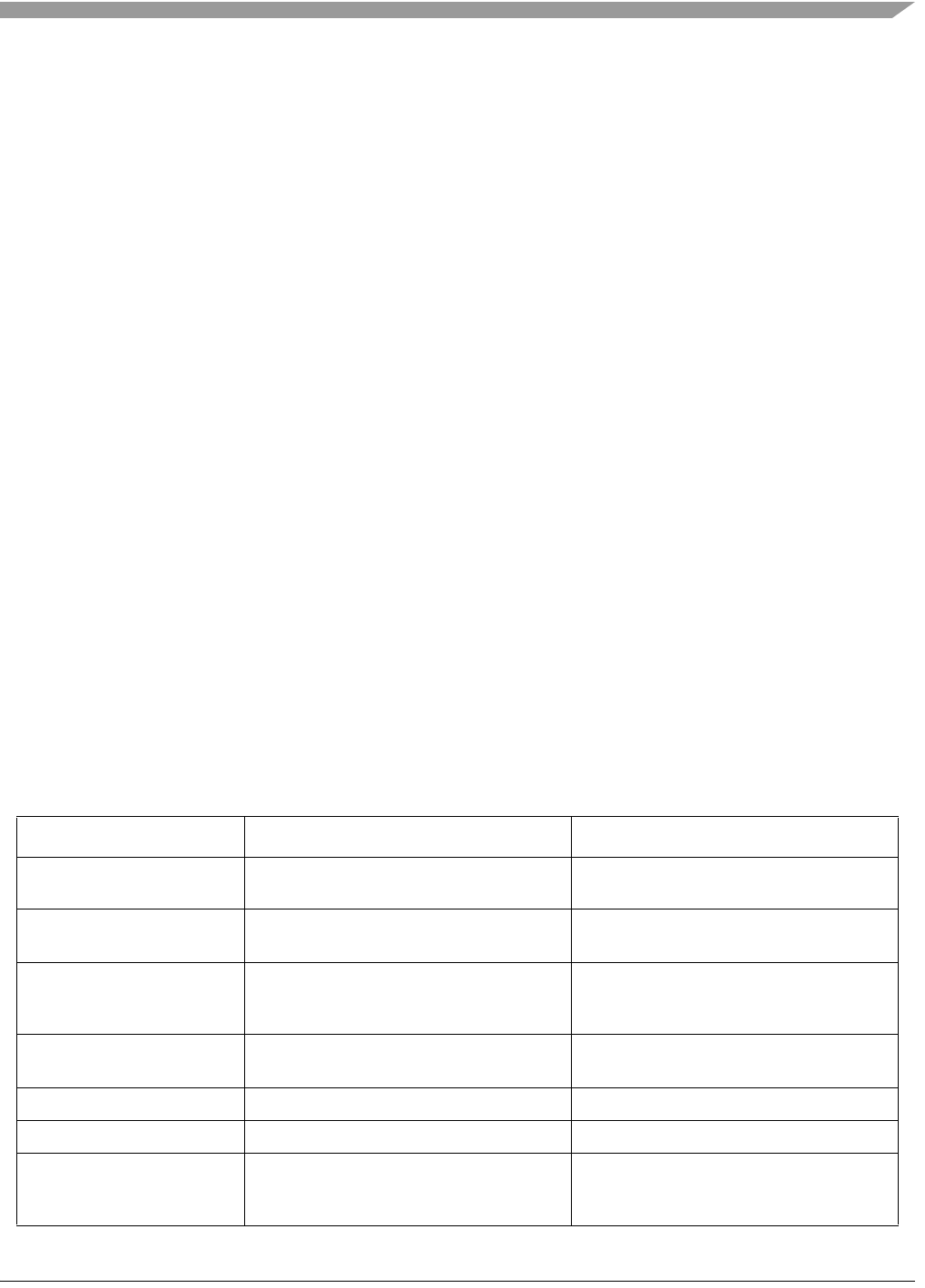

Table 8-1 provides a high-level architectural comparison between HCS08 and ColdFire exception

processing as these differences are important in the definition of the CF1_INTC module. Throughout this

document, the term IRQ refers to an interrupt request and ISR refers to an interrupt service routine to

process an interrupt exception.

Table 8-1. Exception Processing Comparison

Attribute HCS08 V1 ColdFire

Exception Vector Table 32 two-byte entries, fixed location at upper

end of memory

103 four-byte entries, located at lower end of

memory at reset, relocatable with the VBR

More on Vectors 2 for CPU + 30 for IRQs, reset at upper

address

64 for CPU + 39 for IRQs, reset at lowest

address

Exception Stack Frame 5-byte frame: CCR, A, X, PC 8-byte frame: F/V, SR, PC; General-purpose

registers (An, Dn) must be saved/restored

by the ISR

Interrupt Levels 1 = f(CCR[I]) 7= f (SR[I]) with automatic hardware support

for nesting

Non-Maskable IRQ Support No Yes, with level 7 interrupts

Core-enforced IRQ Sensitivity No Level 7 is edge sensitive, else level sensitive

INTC Vectoring Fixed priorities and vector assignments Fixed priorities and vector assignments, plus

any 2 IRQs can be remapped as the highest

priority level 6 requests