MCF51QE128 MCU Series Reference Manual, Rev. 3

176 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

The basic ColdFire interrupt controller supports up to 63 request sources mapped as nine priorities for each

of the seven supported levels (7 levels × 9 priorities per level). Within the nine priorities within a level, the

mid-point is typically reserved for package-level IRQ inputs. The levels and priorities within the level

follow a descending order: 7 > 6 > ... > 1 > 0.

The HCS08 architecture supports a 32-entry exception vector table: the first two vectors are reserved for

internal CPU/system exceptions and the remaining 30 are available for I/O interrupt requests. The

requirement for an exact match between the interrupt requests and priorities across two architectures

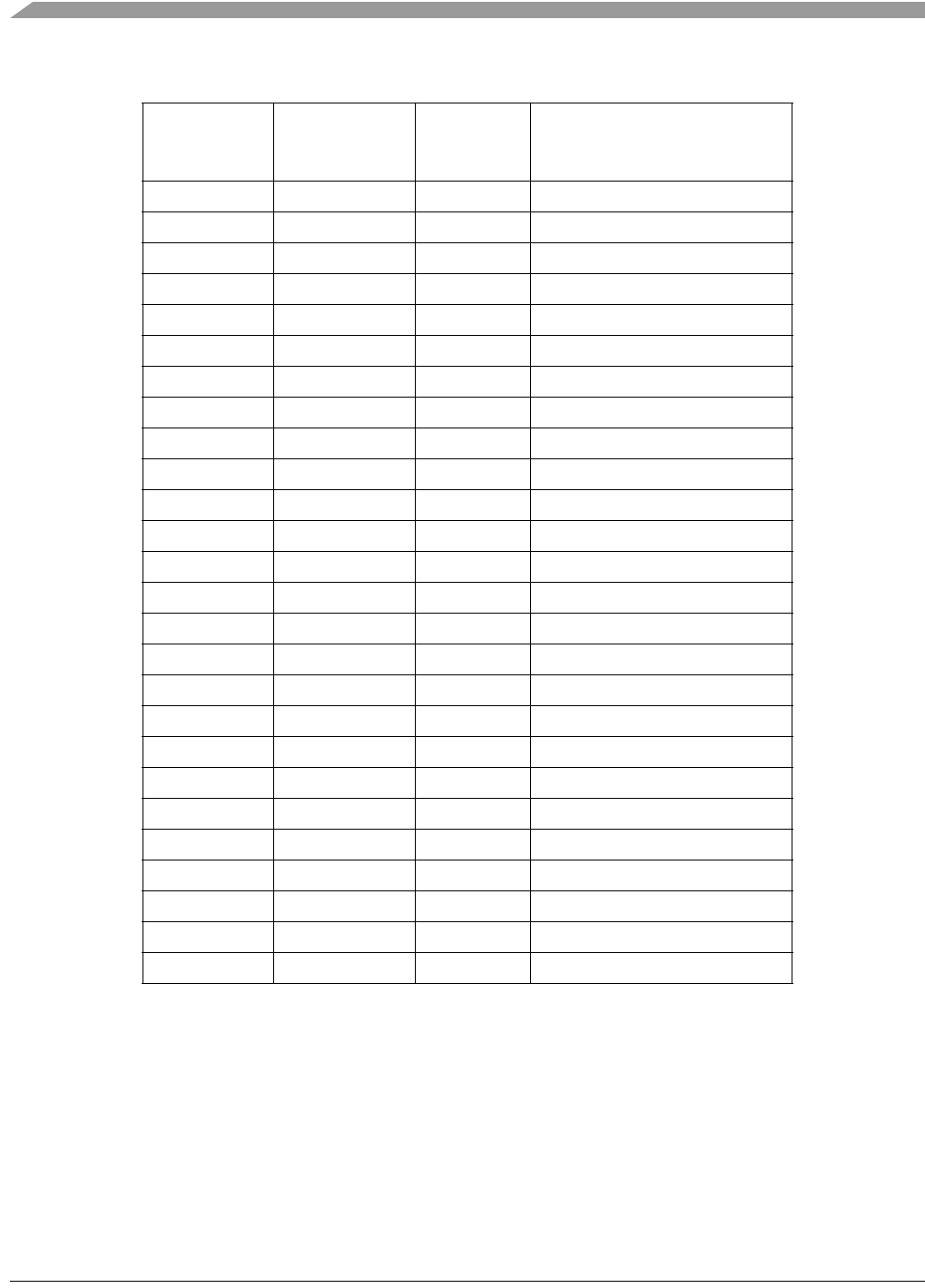

77 0x134 Next SCI1_rx

78 0x138 Next SCI1_tx

79 0x13C Next IICx

80 0x140 Next KBIx

81 0x144 Next ADC

82 0x148 Next ACMPx

83 0x14C Next SCI2_err

84 0x150 Next SCI2_rx

85 0x154 Next SCI2_tx

86 0x158 Next RTC

87 0x15C Next TPM3_ch0

88 0x160 Next TPM3_ch1

89 0x164 Next TPM3_ch2

90 0x168 Next TPM3_ch3

91 0x16C Next TPM3_ch4

92 0x170 Next TPM3_ch5

93 0x174 Next TPM3_ovfl

94–95 0x178–0x17C — Reserved; unused for V1

96 0x180 Next Level 7 Software Interrupt

97 0x184 Next Level 6 Software Interrupt

98 0x188 Next Level 5 Software Interrupt

99 0x18C Next Level 4 Software Interrupt

100 0x190 Next Level 3 Software Interrupt

101 0x194 Next Level 2 Software Interrupt

102 0x198 Next Level 1 Software Interrupt

103–255 0x19C–0x3FC — Reserved; unused for V1

Table 8-2. V1 ColdFire Exception Vector Table (continued)

Vector

Number(s)

Vector

Offset (Hex)

Stacked

Program

Counter

Assignment