MCF51QE128 MCU Series Reference Manual, Rev. 3

28 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 1 Device Overview

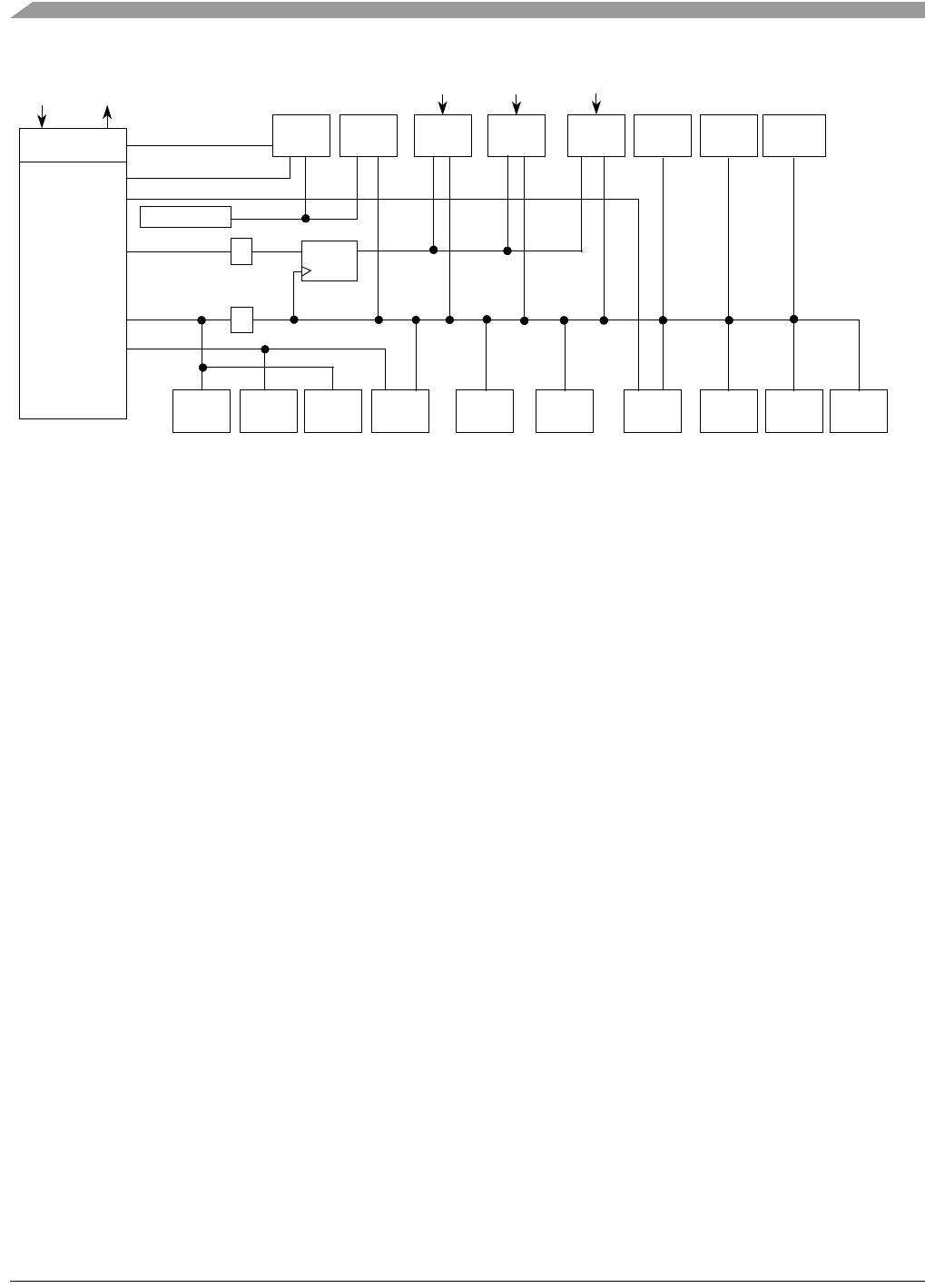

Figure 1-3. System Clock Distribution Diagram

• OSCOUT — This is the direct output of the external oscillator module and can be selected as the

real-time counter clock source. See Chapter 14, “Real-Time Counter (S08RTCV1),” for more

information.

• ICSERCLK — This is the external reference clock and can be selected as the real-time counter

clock source or the alternate clock for the ADC module. Section 11.4.7, “External Reference

Clock,” explains the ICSERCLK in more detail. See Chapter 11, “Analog-to-Digital Converter

(S08ADC12V1),” for more information regarding the use of ICSERCLK with this module.

• ICSIRCLK — This is the internal reference clock and can be selected as the real-time counter clock

source. Section 11.4.6, “Internal Reference Clock,” explains the ICSIRCLK in more detail. See

Chapter 14, “Real-Time Counter (S08RTCV1),” for more information regarding the use of

ICSIRCLK.

• ICSFFCLK — This generates the fixed frequency clock (FFCLK) after being synchronized to the

bus clock. It can be selected as clock source for the TPM modules. The frequency of the

ICSFFCLK is determined by the settings of the ICS. See Section 11.4.8, “Fixed Frequency Clock,”

for details.

• LPOCLK — This clock is generated from an internal low-power oscillator that is completely

independent of the ICS module. The LPOCLK can be selected as the clock source to the RTC or

COP modules. See Chapter 14, “Real-Time Counter (S08RTCV1),” and Section 5.3.1, “Computer

Operating Properly (COP) Watchdog,” for details on using the LPOCLK with these modules.

•TPMxCLK — TPMxCLKs are optional external clock sources for the TPM modules. The

TPMxCLK must be limited to 1/4 the frequency of the bus clock for synchronization. See

Section 16.2.1, “External TPM Clock Sources,” for more details.

TPM1 TPM2 TPM3

SCI1 &

SPI1 &

RAM

CPU &

ADC FLASH GPIO

ICS

ICSOUT

÷2

BUSCLK

ICSLCLK

ICSERCLK

COP

* The fixed frequency clock (FFCLK) is internally

synchronized to the bus clock and must not

exceed one half of the bus clock frequency.

Flash has frequency

requirements for program

and erase operation.

See the MCF51QE128

Data Sheet for details.

ADC has min and max

frequency requirements.

See the ADC chapter

and the MCF51QE128

Data Sheet for details.

XOSC

EXTAL

XTAL

ACMP1 &

FFCLK*

ICSFFCLK

RTC

TPM1CLK

ICSIRCLK

÷2

PMC

IIC1 &

TPM3CLK

TPM2CLK

SYNC*

LPOCLK

BDC

1KHz LPO

OSCOUT

Debug

SCI2

SPI2 ACMP2

IIC2

INTC

RGPIO