MCF51QE128 MCU Series Reference Manual, Rev. 3

122 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 6 Parallel Input/Output Control

6.7.2.3 Port B Pull Enable Register (PTBPE)

The port B pull enable register enables pull-ups on the corresponding PTB pin. In some cases, a pull-down

device is enabled if pull-downs are supported by an alternate pin function (e.g., KBI).

6.7.2.4 Port B Slew Rate Enable Register (PTBSE)

Table 6-7. PTBDD Register Field Descriptions

Field Description

7–0

PTBDDn

Data Direction for Port B Bits. These read/write bits control the direction of port B pins and what is read for PTBD

reads.

0 Input (output driver disabled) and reads return the pin value.

1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.

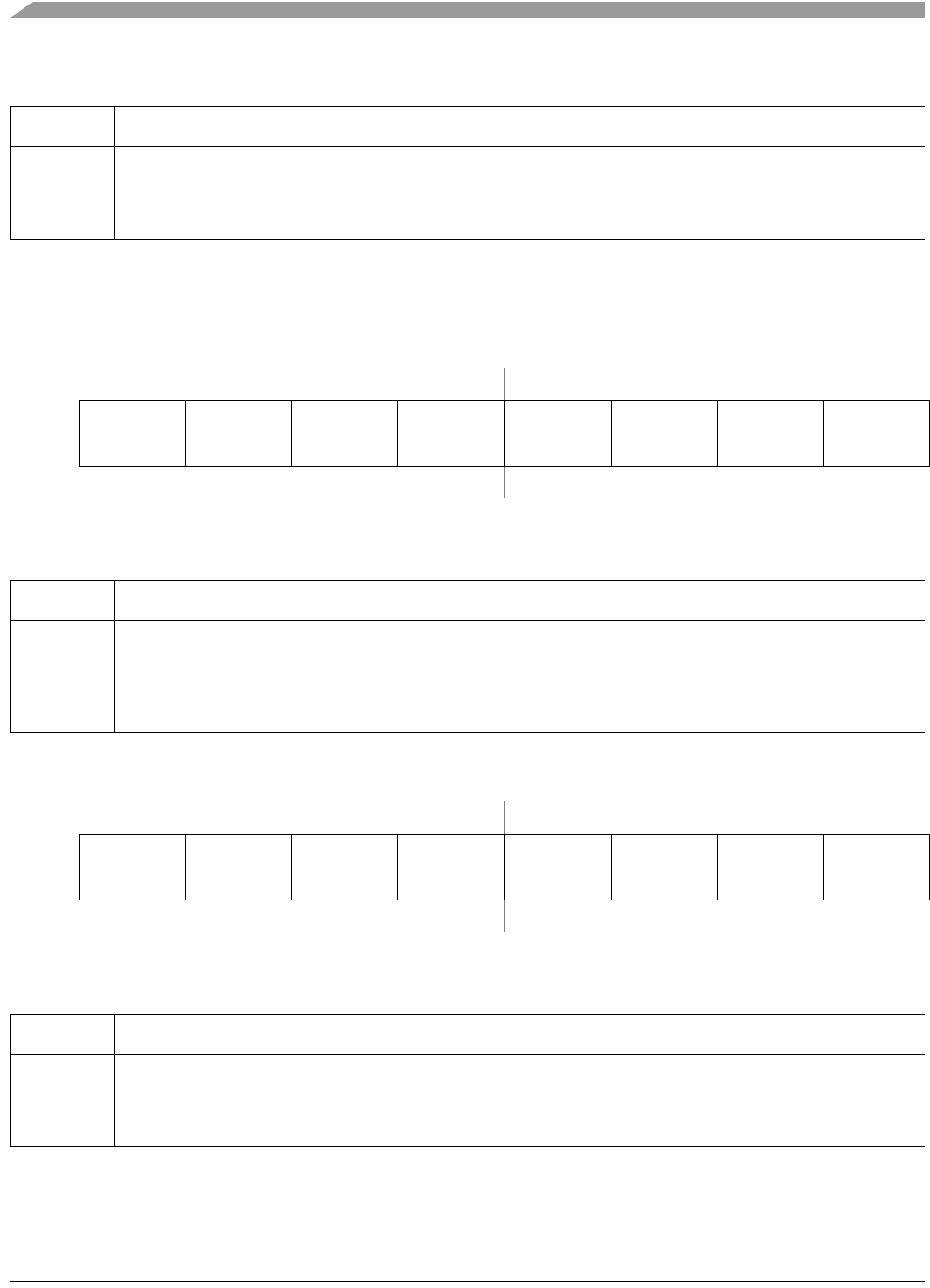

76543210

R

PTBPE7 PTBPE6 PTBPE5 PTBPE4 PTBPE3 PTBPE2 PTBPE1 PTBPE0

W

Reset:00000000

Figure 6-11. Internal Pull Enable for Port B Register (PTBPE)

Table 6-8. PTBPE Register Field Descriptions

Field Description

7–0

PTBPEn

Internal Pull Enable for Port B Bits. Each of these control bits determines if the internal pull-up or pull-down device

is enabled for the associated PTB pin. For port B pins configured as outputs, these bits have no effect and the

internal pull devices are disabled.

0 Internal pull-up/pull-down device disabled for port B bit n.

1 Internal pull-up/pull-down device enabled for port B bit n.

76543210

R

PTBSE7 PTBSE6 PTBSE5 PTBSE4 PTBSE3 PTBSE2 PTBSE1 PTBSE0

W

Reset:00000000

Figure 6-12. Slew Rate Enable for Port B Register (PTBSE)

Table 6-9. PTBSE Register Field Descriptions

Field Description

7–0

PTBSEn

Output Slew Rate Enable for Port B Bits. Each of these control bits determines if the output slew rate control is

enabled for the associated PTB pin. For port B pins configured as inputs, these bits have no effect.

0 Output slew rate control disabled for port B bit n.

1 Output slew rate control enabled for port B bit n.