Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 363

Get the latest version from freescale.com

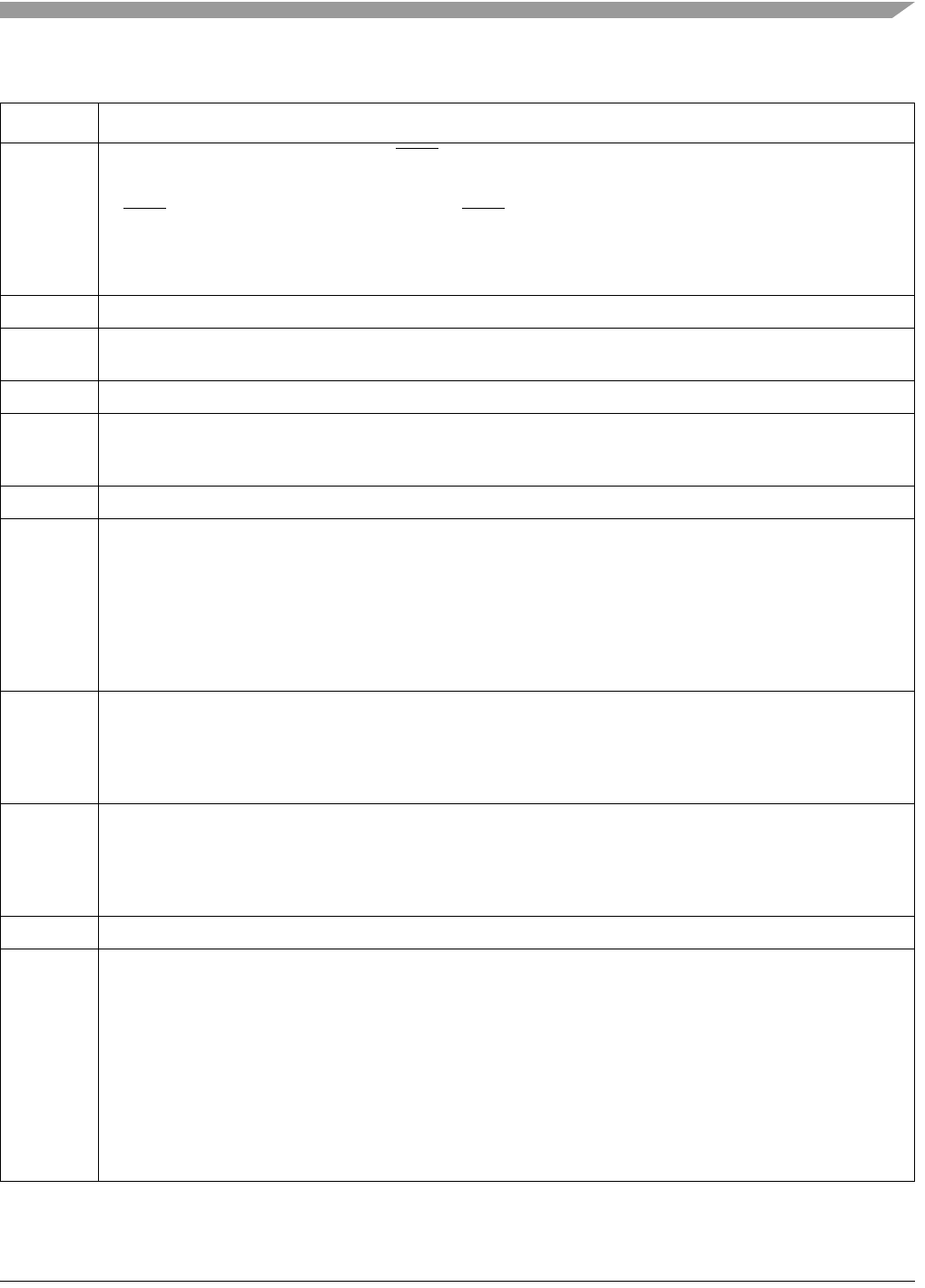

18

BKD

Breakpoint disable. Disables the normal BKPT

input signal and BACKGROUND command functionality, and

allows the assertion of this pin (or execution of the BACKGROUND command) to generate a debug interrupt.

0 Normal operation

1 BKPT

is edge-sensitive: a high-to-low edge on BKPT or the receipt of a BDM BACKGROUND command

signals a debug interrupt to the ColdFire core. The processor makes this interrupt request pending until the

next sample point occurs, when the exception is initiated. In the ColdFire architecture, the interrupt sample

point occurs once per instruction. There is no support for nesting debug interrupts.

17 Reserved, must be cleared.

16

IPW

Inhibit processor writes. Inhibits processor-initiated writes to the debug module’s programming model registers.

IPW can be modified only by commands from the BDM interface.

15 Reserved, must be cleared.

14

TRC

Force emulation mode on trace exception.

0 Processor enters supervisor mode.

1 Processor enters emulator mode when a trace exception occurs.

13 Reserved, must be cleared.

12–11

DDC

Debug data control. Controls peripheral bus operand data capture for DDATA, which displays the number of bytes

defined by the operand reference size (a marker) before the actual data; byte displays 8 bits, word displays 16

bits, and long displays 32 bits (one nibble at a time across multiple PSTCLK clock cycles). See Table 18-26. A

non-zero value enables partial data trace capabilities.

00 No operand data is displayed.

01 Capture all write data.

10 Capture all read data.

11 Capture all read and write data.

10

UHE

User halt enable. Selects the CPU privilege level required to execute the HALT instruction. The core must be

operating with XCSR[ENBDM] set to execute any HALT instruction, else the instruction is treated as an illegal

opcode.

0 HALT is a supervisor-only instruction.

1 HALT is a supervisor/user instruction.

9–8

BTB

Branch target bytes. Defines the number of bytes of branch target address DDATA displays. See Section 18.4.3.1,

“Begin Execution of Taken Branch (PST = 0x05).”

00 No target address capture

01 Lower 2 bytes of the target address

1x Lower 3 bytes of the target address

7 Reserved, must be cleared.

6

NPL

Non-pipelined mode. Determines if the core operates in pipelined mode.

0 Pipelined mode

1 Non-pipelined mode. The processor effectively executes one instruction at a time with no overlap. This typically

adds five cycles to the execution time of each instruction. Given an average execution latency of ~2 cycles per

instruction, throughput in non-pipeline mode would be ~7 cycles per instruction, approximately 25% - 33% of

pipelined performance.

Regardless of the NPL state, a triggered PC breakpoint is always reported before the triggering instruction

executes. In normal pipeline operation, the occurrence of an address and/or data breakpoint trigger is imprecise.

In non-pipeline mode, these triggers are always reported before the next instruction begins execution and trigger

reporting can be considered precise.

Table 18-5. CSR Field Descriptions (continued)

Field Description