ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

152 Freescale Semiconductor

7.2.8 Status Register (SR)

The SR stores the processor status and includes the CCR, the interrupt priority mask, and other control

bits. In supervisor mode, software can access the entire SR. In user mode, only the lower 8 bits (CCR) are

accessible. The control bits indicate the following states for the processor: trace mode (T bit), supervisor

or user mode (S bit), and master or interrupt state (M bit). All defined bits in the SR have read/write access

when in supervisor mode. The lower byte of the SR (the CCR) must be loaded explicitly after reset and

before any compare (CMP), Bcc, or Scc instructions execute.

27

BWD

Buffered peripheral bus write disable.

0 Peripheral bus writes are buffered and the bus cycle is terminated immediately and does not wait for the peripheral

bus termination status.

1 Disables the buffering of peripheral bus writes and does not terminate the bus cycle until a registered version of

the peripheral bus termination is received.

Note: If buffered writes are enabled (BWD = 0), any peripheral bus error status is lost.

26 Reserved, should be cleared.

25

FSD

Flash speculation disabled. Disables certain performance-enhancing features related to address speculation in the

flash memory controller.

0 The flash controller tries to speculate on read accesses to improve processor performance by minimizing the

exposed flash memory access time. Recall the basic flash access time is two processor cycles.

1 Certain flash address speculation is disabled.

24–0 Reserved, should be cleared.

BDM: Load: 0xEE (SR)

Store: 0xCE (SR)

Access: Supervisor read/write

BDM read/write

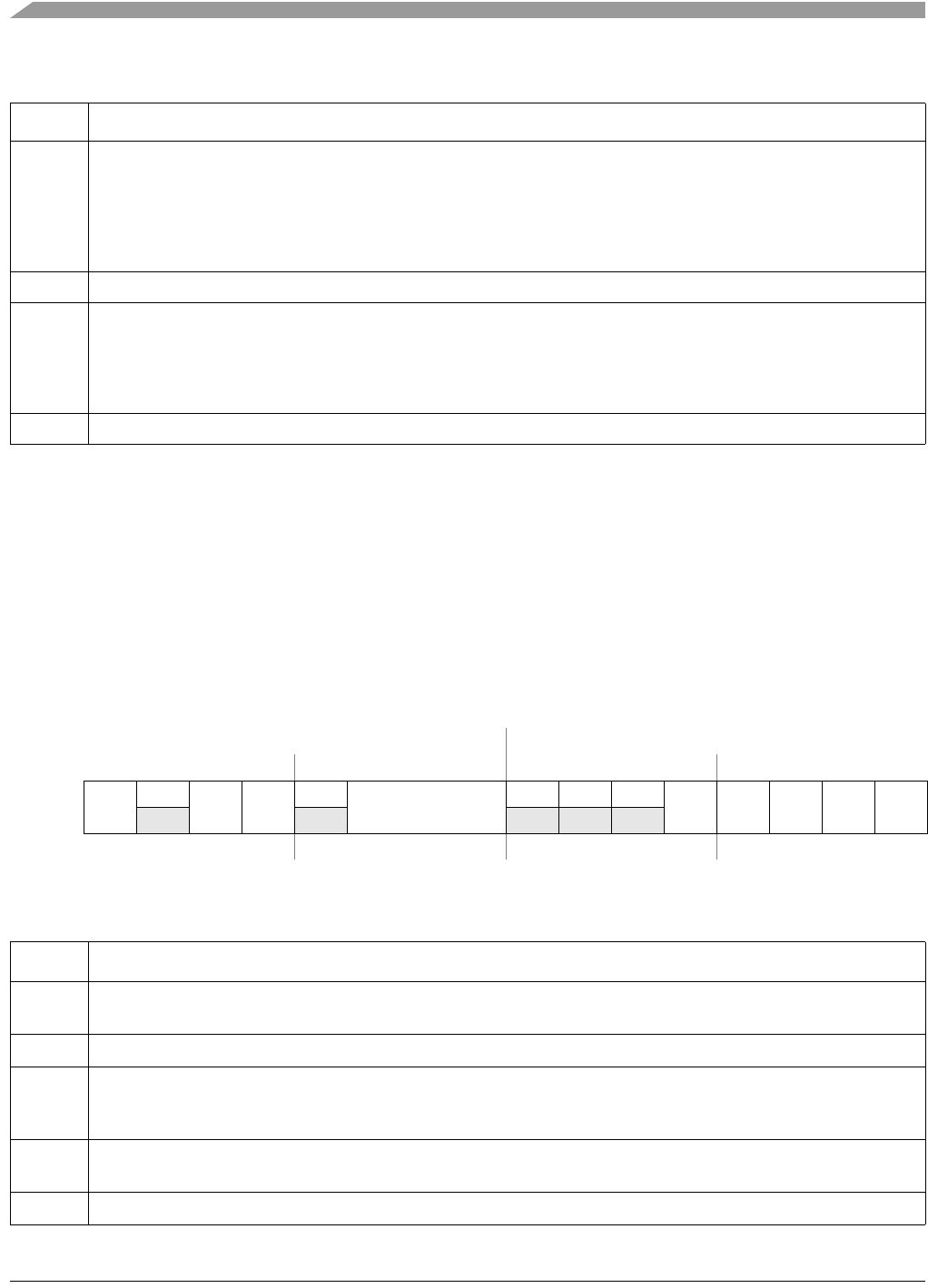

System Byte Condition Code Register (CCR)

1514131211109876543210

R

T

0

S M

0

I

000

X N ZVC

W

Reset00100111000—————

Figure 7-9. Status Register (SR)

Table 7-4. SR Field Descriptions

Field Description

15

T

Trace enable. When set, the processor performs a trace exception after every instruction.

14 Reserved, must be cleared.

13

S

Supervisor/user state.

0User mode

1 Supervisor mode

12

M

Master/interrupt state. Bit is cleared by an interrupt exception and software can set it during execution of the RTE or

move to SR instructions.

11 Reserved, must be cleared.

Table 3. CPUCR Field Descriptions (continued)

Field Description