MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 301

Get the latest version from freescale.com

15.2.4 SCI Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do

not involve writing to this register) clear these status flags.

2

RE

Receiver Enable. When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin. If

LOOPS is set the RxD pin reverts to being a general-purpose I/O pin even if RE is set.

0 Receiver off.

1 Receiver on.

1

RWU

Receiver Wakeup Control. This bit can be written to 1 to place the SCI receiver in a standby state where it waits

for automatic hardware detection of a selected wakeup condition. The wakeup condition is an idle line between

messages (WAKE = 0, idle-line wakeup) or a logic 1 in the most significant data bit in a character (WAKE = 1,

address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition

automatically clears RWU. Refer to Section 15.3.3.2, “Receiver Wakeup Operation,” for more details.

0 Normal SCI receiver operation.

1 SCI receiver in standby waiting for wakeup condition.

0

SBK

Send Break. Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional

break characters of 10 or 11 (13 or 14 if BRK13 = 1) bit times of logic 0 are queued as long as SBK is set.

Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a

second break character may be queued before software clears SBK. Refer to Section 15.3.2.1, “Send Break and

Queued Idle” for more details.

0 Normal transmitter operation.

1 Queue break character(s) to be sent.

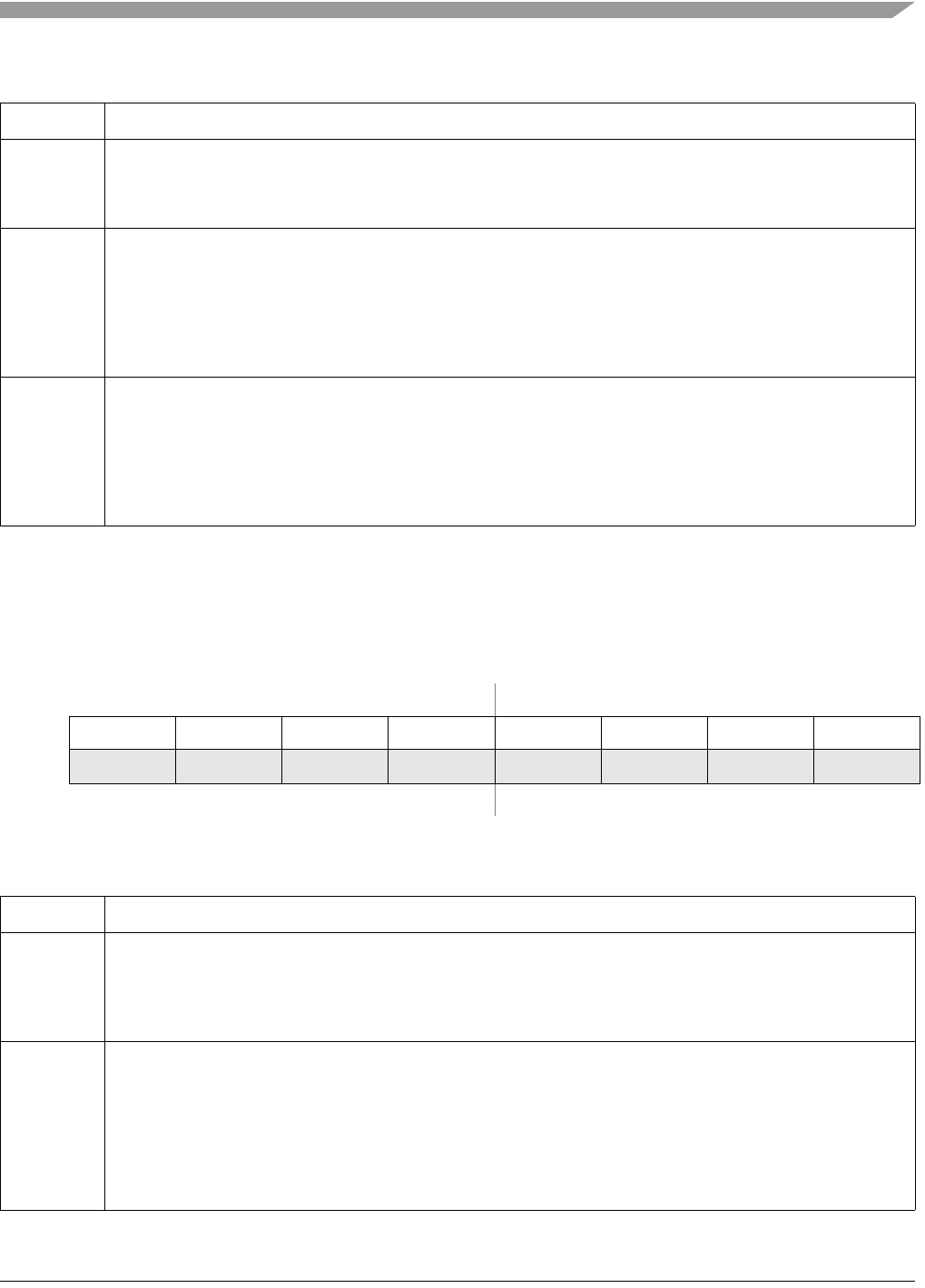

76543210

R TDRE TC RDRF IDLE OR NF FE PF

W

Reset11000000

Figure 15-9. SCI Status Register 1 (SCIxS1)

Table 15-5. SCIxS1 Field Descriptions

Field Description

7

TDRE

Transmit Data Register Empty Flag. TDRE is set out of reset and when a transmit data value transfers from the

transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read

SCIxS1 with TDRE set and then write to the SCI data register (SCIxD).

0 Transmit data register (buffer) full.

1 Transmit data register (buffer) empty.

6

TC

Transmission Complete Flag. TC is set out of reset and when TDRE is set and no data, preamble, or break

character is being transmitted.

0 Transmitter active (sending data, a preamble, or a break).

1 Transmitter idle (transmission activity complete).

TC is cleared automatically by reading SCIxS1 with TC set and then doing one of the following:

• Write to the SCI data register (SCIxD) to transmit new data

• Queue a preamble by changing TE from 0 to 1

• Queue a break character by writing 1 to SBK in SCIxC2

Table 15-4. SCIxC2 Field Descriptions (continued)

Field Description