Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 379

Get the latest version from freescale.com

18.3.10 Data Breakpoint and Mask Registers (DBR, DBMR)

DBR specifies data patterns used as part of the trigger into debug mode. DBR bits are masked by setting

corresponding DBMR bits, as defined in TDR.

DBR and DBMR are accessible in supervisor mode using the WDEBUG instruction and through the BDM

port using the WRITE_DREG commands.

The DBR supports aligned and misaligned references. Table 18-22 shows the relationships between

processor address, access size, and location within the 32-bit data bus.

Table 18-19. ABHR Field Description

Field Description

31–0

Address

High address. Holds the 32-bit address marking the upper bound of the address breakpoint range.

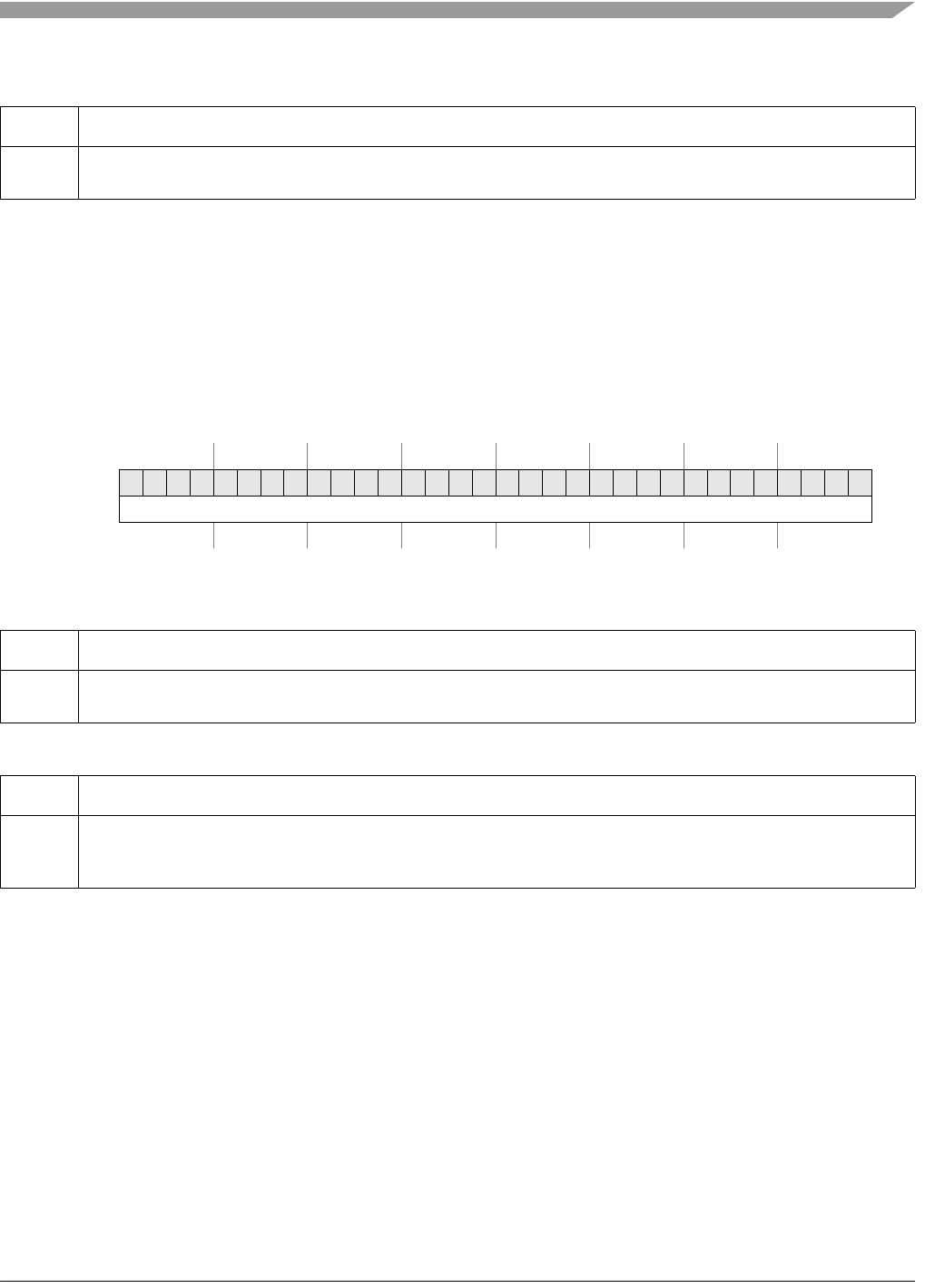

DRc[4:0]: 0x0E (DBR)

0x0F (DBMR)

Access: Supervisor write-only

BDM write-only

313029282726252423222120191817161514131211109876543210

R

W Data (DBR); Mask (DBMR)

Reset00000000000000000000000000000000

Figure 18-14. Data Breakpoint & Mask Registers (DBR, DBMR)

Table 18-20. DBR Field Descriptions

Field Description

31–0

Data

Data breakpoint value. Contains the value to be compared with the data value from the processor’s local bus as a

breakpoint trigger.

Table 18-21. DBMR Field Descriptions

Field Description

31–0

Mask

Data breakpoint mask. The 32-bit mask for the data breakpoint trigger.

0 The corresponding DBR bit is compared to the appropriate bit of the processor’s local data bus

1 The corresponding DBR bit is ignored