Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 405

Get the latest version from freescale.com

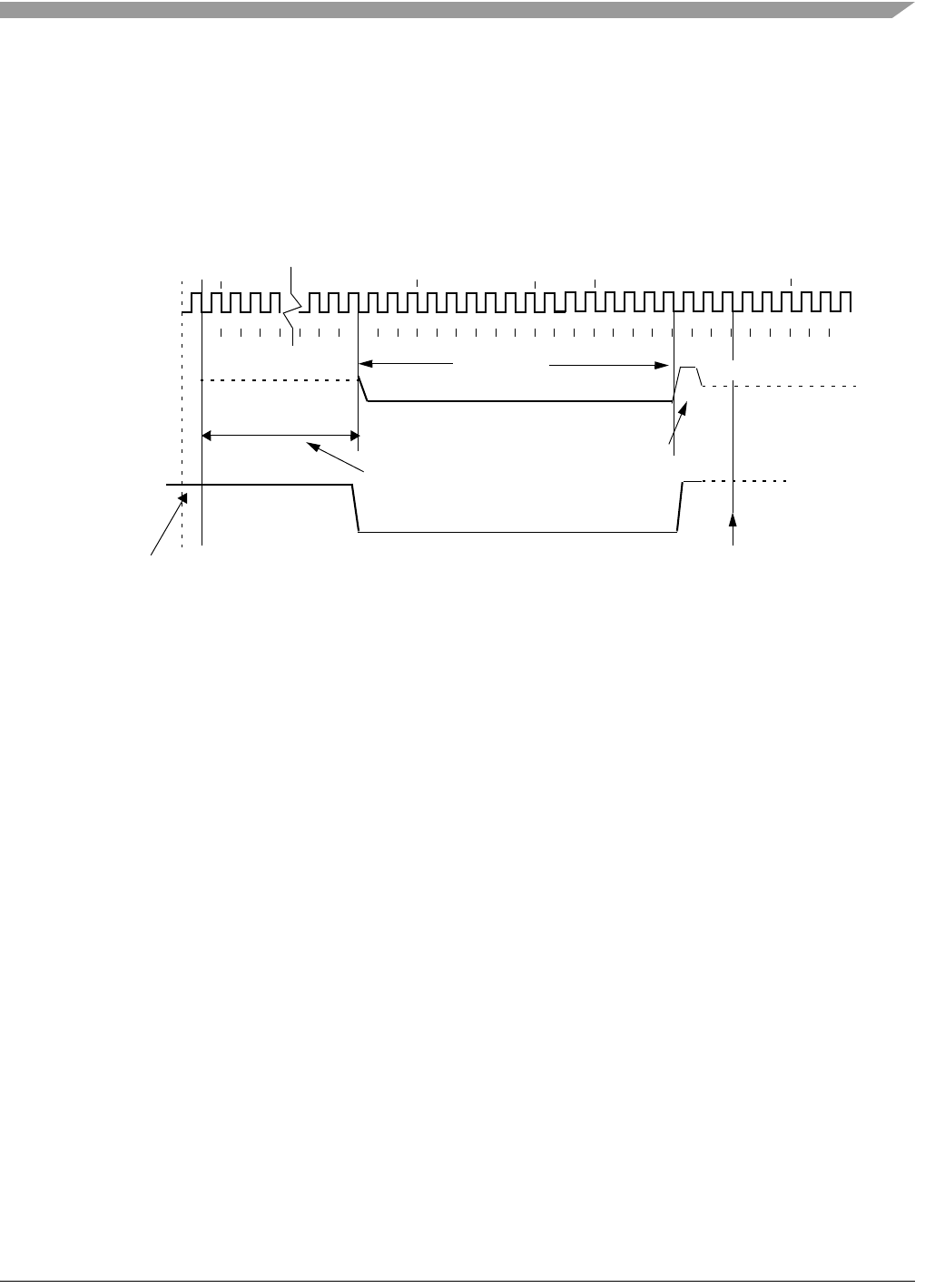

clock cycles after the BDC command was issued. The end of the BDC command is assumed to be the 16th

BDC clock cycle of the last bit. This minimum delay assures enough time for the host to recognize the

ACK pulse. Note that there is no upper limit for the delay between the command and the related ACK

pulse, since the command execution depends on the CPU bus frequency, which in some cases could be

very slow compared to the serial communication rate. This protocol allows great flexibility for pod

designers, since it does not rely on any accurate time measurement or short response time to any event in

the serial communication.

Figure 18-19. Target Acknowledge Pulse (ACK)

NOTE

If the ACK pulse was issued by the target, the host assumes the previous

command was executed. If the CPU enters a stop mode prior to executing a

non-intrusive command, the command is discarded and the ACK pulse is

not issued. After entering a stop mode, the BDC command is no longer

pending and the XCSR[CSTAT] value of 001 is kept until the next command

is successfully executed.

Figure 18-20 shows the ACK handshake protocol in a command level timing diagram. A READ_MEM.B

command is used as an example:

1. The 8-bit command code is sent by the host, followed by the address of the memory location to be

read.

2. The target BDC decodes the command and sends it to the CPU.

3. Upon receiving the BDC command request, the CPU schedules a execution slot for the command.

4. The CPU temporarily stalls the instruction stream at the scheduled point, executes the

READ_BYTE command and then continues.

This process is referred to as cycle stealing. The READ_MEM.B appears as a single-cycle operation to the

processor, even though the pipelined nature of the Operand Execution Pipeline requires multiple CPU

clock cycles for it to actually complete. After that, the debug module tracks the execution of the

READ_MEM.b command as the processor resumes the normal flow of the application program. After

detecting the READ_MEM.B command is done, the BDC issues an ACK pulse to the host controller,

16 CYCLES

BDC CLOCK

(TARGET MCU)

TA RG ET

TRANSMITS

HIGH-IMPEDANCE

BKGD PIN

HIGH-IMPEDANCE

MINIMUM DELAY

FROM THE BDC COMMAND

32 CYCLES

EARLIEST

START OF

NEXT BIT

SPEED UP PULSE

16th CYCLE OF THE

LAST COMMAD BIT

ACK PULSE