MCF51QE128 MCU Series Reference Manual, Rev. 3

30 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 1 Device Overview

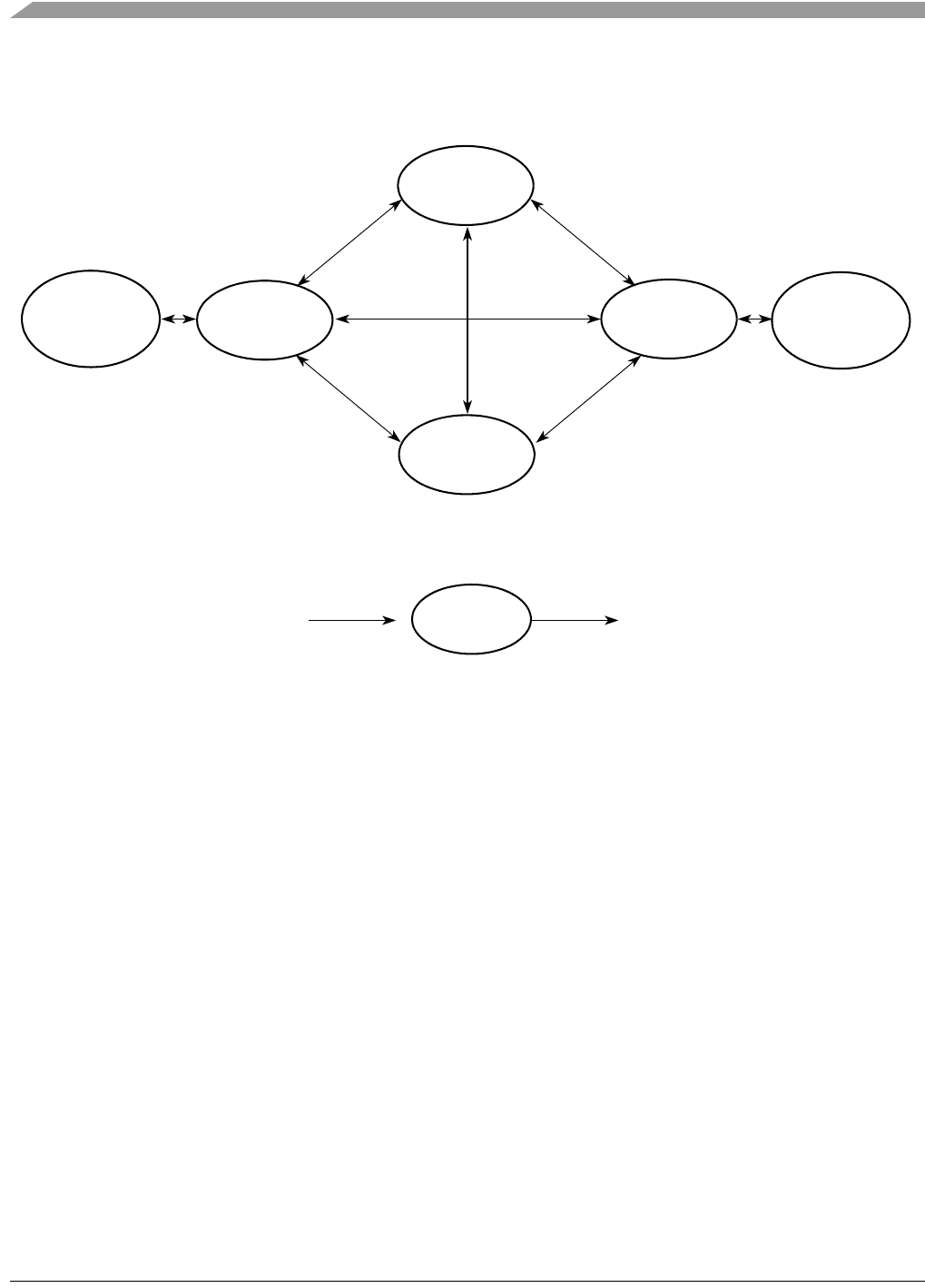

Figure 1-4. ICS Modes of Operation

1.4.3.6 FLL Bypassed External Low-Power (FBELP)

In FLL bypassed external low-power mode, the FLLs are disabled and bypassed, and the ICS supplies a

clock derived from the external reference clock. The external reference clock can be an external

crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source.

1.4.3.7 Stop (STOP)

In stop mode, the FLLs are disabled and the internal or external reference clocks can be selected to be

enabled or disabled. The ICS does not provide an MCU clock source unless the debug ENBDM bit is set.

FLL Bypassed

Internal Low-

Power(FBILP)

IREFS=1

CLKS=00

LP=0

Entered from any state when

MCU enters stop with

ENBDM=0.

FLL Engaged

Internal (FEI)

FLL Bypassed

Internal (FBI)

FLL Bypassed

External (FBE)

FLL Engaged

External (FEE)

FLL Bypassed

External Low-

Power(FBELP)

IREFS=0

CLKS=00

LP=0

IREFS=0

CLKS=10

LP=0

Returns to state that was active

before MCU entered stop, unless

reset occurs while in stop.

IREFS=0

CLKS=10

LP=1

IREFS=1

CLKS=01

LP=0

IREFS=1

CLKS=01

LP=1

Stop