MCF51QE128 MCU Series Reference Manual, Rev. 3

320 Freescale Semiconductor

Get the latest version from freescale.com

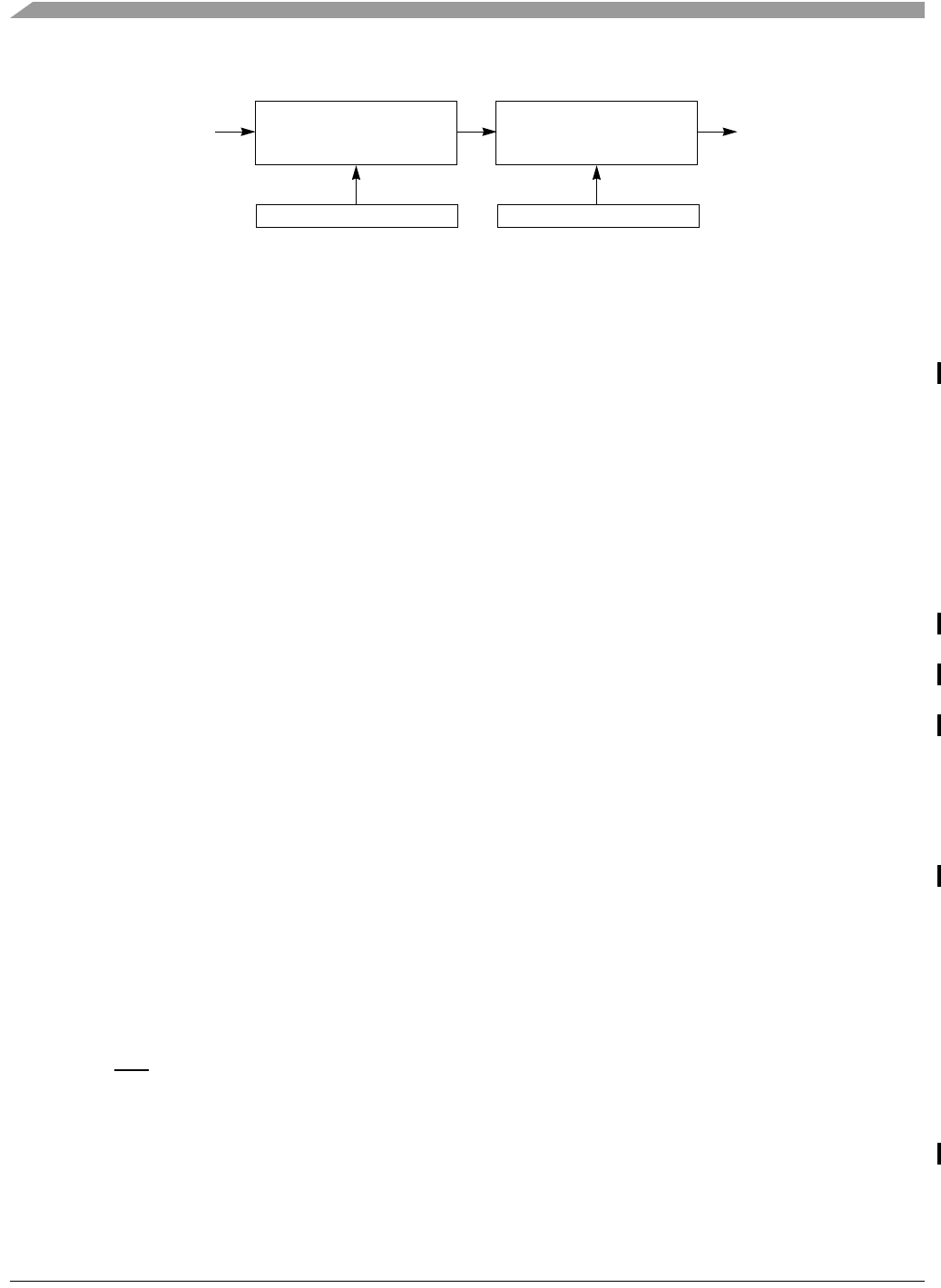

Figure 16-4. SPI Baud Rate Generation

16.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control

bits. When the SPI is disabled (SPIxC1[SPE] is cleared), these four pins revert to being general-purpose

port I/O pins that are not controlled by the SPI.

16.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master,

this pin is the serial clock output.

16.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero bit (SPIxC2[SPC0]) is cleared (not

bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and

SPIxC2[SPC0] is cleared, this pin is the serial data input. If SPC0 is set to select single-wire bidirectional

mode and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the

bidirectional mode output enable bit determines whether the pin acts as an input (SPIxC2[BIDIROE] = 0)

or an output (BIDIROE = 1). If SPC0 is set and slave mode is selected, this pin is not used by the SPI and

reverts to a general-purpose port I/O pin.

16.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPIxC2[SPC0]) is cleared (not bidirectional

mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 is cleared, this pin is

the serial data output. If SPC0 is set to select single-wire bidirectional mode and slave mode is selected,

this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit

determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 is set

and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O

pin.

16.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as

a master and mode fault enable is off (SPIxC2[MODFEN] = 0), this pin is not used by the SPI and reverts

to a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN is set, the slave select

Divide By

2, 4, 8, 16, 32, 64, 128, or 256

Divide By

1, 2, 3, 4, 5, 6, 7, or 8

Prescaler Clock Rate Divider

SPIxBR[SPPR] SPIxBR[SPR]

Bus Clock

Master

SPI

Bit Rate