MCF51QE128 MCU Series Reference Manual, Rev. 3

58 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 4 Memory

Regions within the memory map are subject to restrictions with regard to the types of allowable accesses.

These are outlined in Table 4-1. Non-supported access types terminate the bus cycle with an error and

would typically generate a system reset in response to the error termination.

Consistent with past ColdFire devices, flash configuration data is located at 0x400.

The slave peripherals section of the memory map is further broken into the following sub-sections:

0x(FF)FF_8000 – 0x(FF)FF_807F Direct-page peripheral regs

0x(FF)FF_9800 – 0x(FF)FF_98FF High-page peripheral regs

0x(FF)FF_FFC0 – 0x(FF)FF_FFFC Interrupt controller

The section of memory at 0x(00)C0_0000 is assigned for use by the ColdFire Rapid GPIO module. See

Section 4.2.2, “ColdFire Rapid GPIO Memory Map,” for the rapid GPIO memory map and Section 6.4,

“V1 ColdFire Rapid GPIO Functionality,” for further details on the module.

The MCF51QE128/64/32 devices utilize an 8-bit peripheral bus. The bus bridge from the ColdFire system

bus to the peripheral bus is capable of serializing 16-bit accesses into two 8-bit accesses. This can be used

to speed access to properly aligned peripheral registers. Note, not all peripheral registers are aligned to take

advantage of this feature.

CPU accesses to those parts of the memory map marked as unimplemented in Figure 4-1 result in an illegal

address reset if CPUCR[ARD] is cleared or an address error exception if CPUCR[ARD] is set.

The lower 32K of flash memory and slave peripherals sections of the memory map are most efficiently

accessed using the ColdFire absolute short addressing mode. RAM is most efficiently accessed using the

A5-relative addressing mode (address register indirect with displacement mode).

4.2 Register Addresses and Bit Assignments

Peripheral registers in the MCF51QE128/64/32 are divided into two groups:

• Direct-page registers are located at 0x(FF)FF_8000 in the memory map.

• High-page registers are located at 0x(FF)FF_9800 in the memory map.

There is no functional advantage to locating peripherals in the direct page versus the high page

peripheral space for the MCF51QE128/64/32. Both sets of registers may be efficiently accessed

using the ColdFire absolute short addressing mode. The areas are differentiated to maintain

documentation compatibility with the MC9S08QE128/64/32, where there are significant

performance issues.

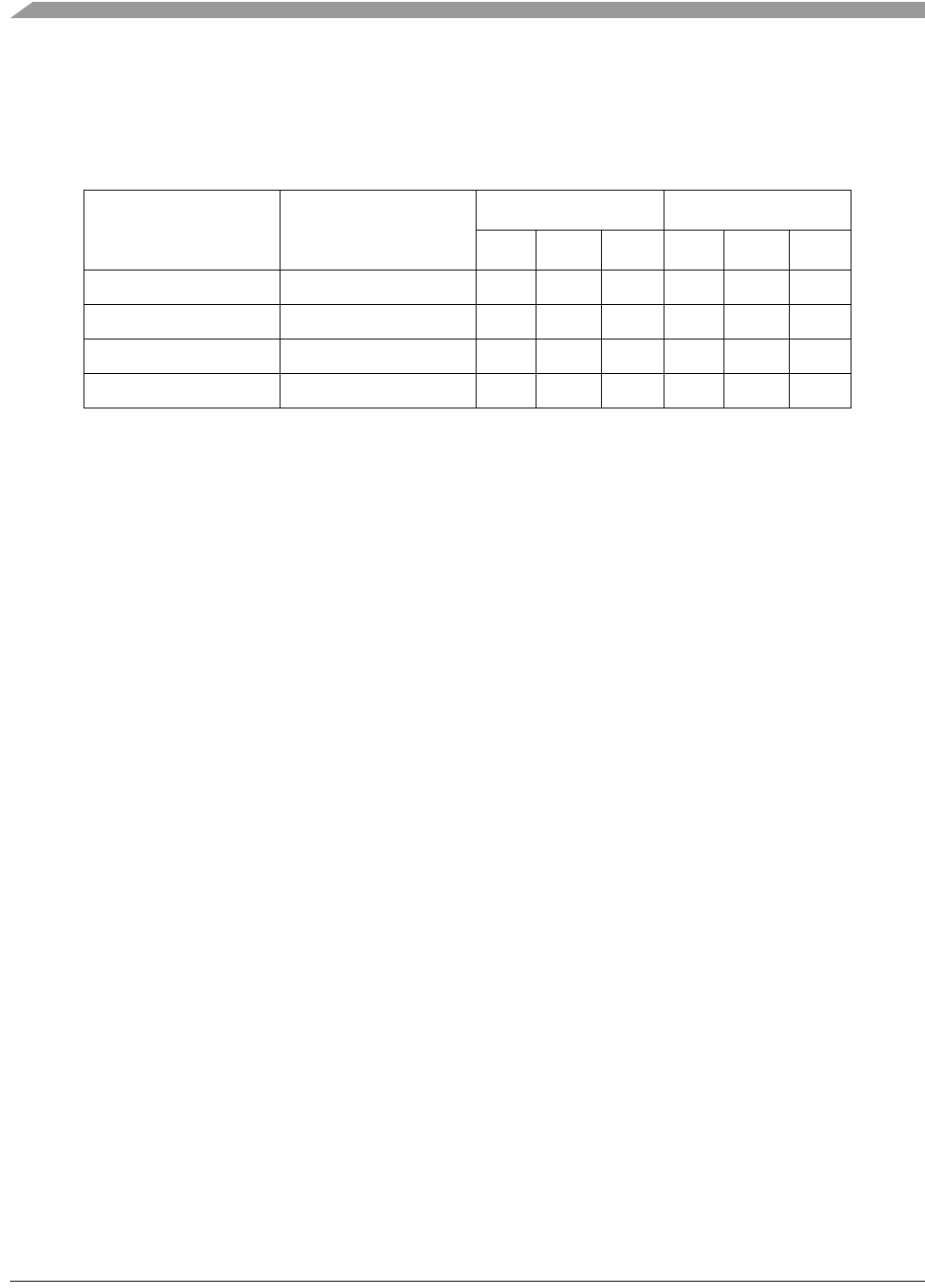

Table 4-1. CPU Access Type Allowed by Region

Base Address Region

Read Write

Byte Word Long Byte Word Long

0x(00)00_0000

Flash

xxx——x

0x(00)80_0000

RAM

xxxxxx

0x(00)C0_0000

Rapid GPIO

xxxxxx

0x(FF)FF_8000

Peripherals

xx—xx—