Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 403

Get the latest version from freescale.com

Write data at the specified memory address. The reference address is transmitted as three 8-bit packets

(msb to lsb) immediately after the command packet. The access attributes are defined by BAAR[TT,TM].

The hardware forces low-order address bits to zeros for word and longword accesses to ensure these

accesses are on 0-modulo-size alignments. If the with-status option is specified, the core status byte

contained in XCSR[31–24] (XCSR_SB) is returned before the read data. The XCSR status byte reflects

the state after the memory read was performed.

The examples show the WRITE_MEM.B{_WS}, WRITE_MEM.W{_WS}, and WRITE_MEM.L{_WS}

commands.

18.4.1.5.21 WRITE_Rn

If the processor is halted, this command writes the 32-bit operand to the selected CPU general-purpose

register (An, Dn). See Table 18-24 for the CRN details when CRG is 01.

If the processor is not halted, this command is rejected as an illegal operation and no operation is

performed.

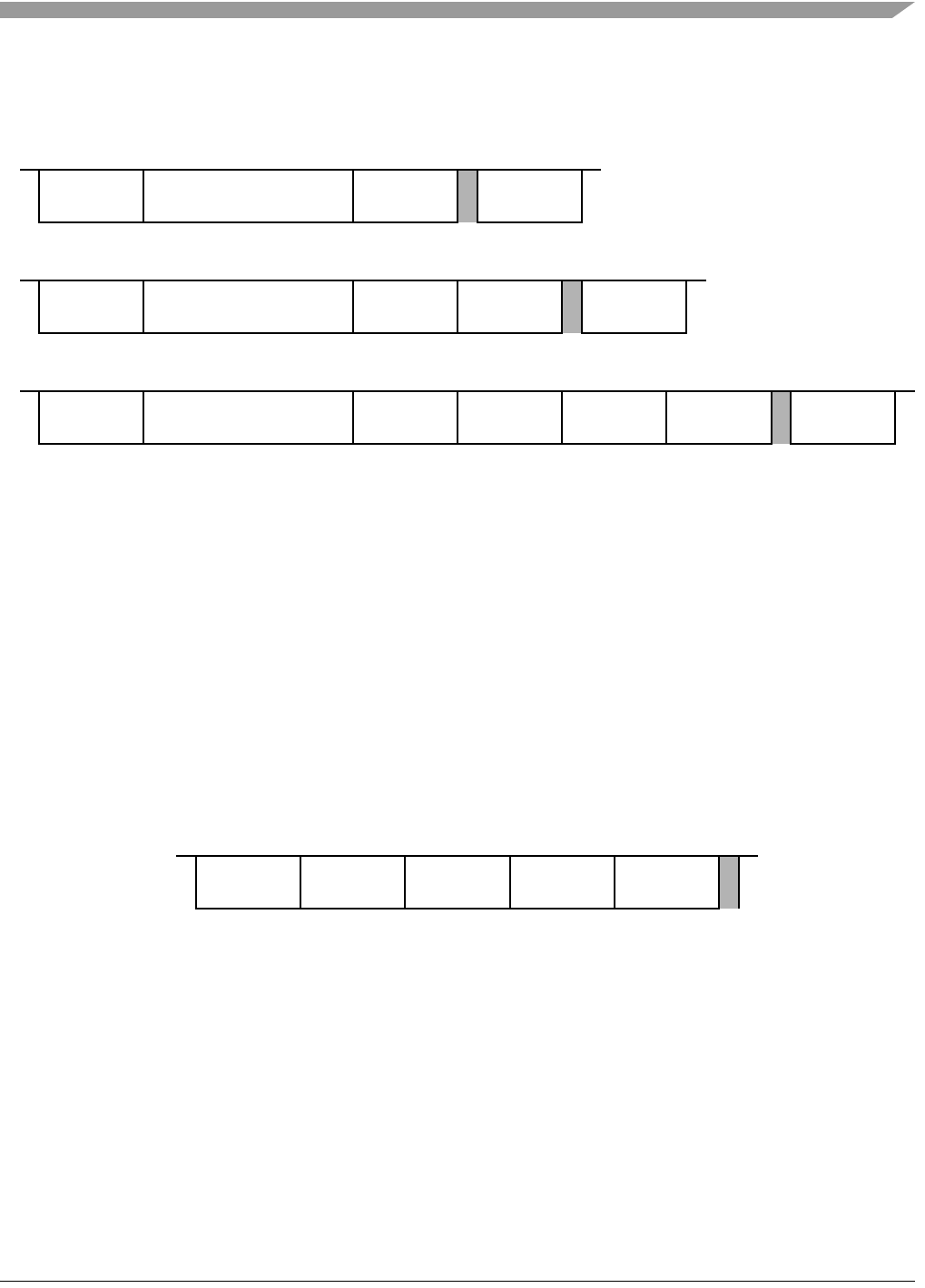

WRITE_MEM.sz_WS

Write memory at the specified address with status Non-intrusive

0x11 Address[23-0]

Memory

data[7–0]

XCSR_SB

host →

target

host →

target

host →

target

D

L

Y

target →

host

0x15 Address[23-0]

Memory

data[15–8]

Memory

data[7–0]

XCSR_SB

host →

target

host →

target

host →

target

host →

target

D

L

Y

target →

host

0x19 Address[23-0]

Memory

data[31–24]

Memory

data[23–16]

Memory

data[15–8]

Memory

data[7–0]

XCSR_SB

host →

target

host →

target

host →

target

host →

target

host →

target

host →

target

D

L

Y

target →

host

Write general-purpose CPU register Active Background

0x40+CRN

Rn data

[31–24]

Rn data

[23–16]

Rn data

[15–8]

Rn data

[7–0]

host →

target

host →

target

host →

target

host →

target

host →

target

D

L

Y