ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

160 Freescale Semiconductor

7.3.3.3 Illegal Instruction Exception

The default operation of the V1 ColdFire processor is the generation of an illegal opcode reset event if an

illegal instruction is detected. If CPUCR[IRD] is set, the reset is disabled and a processor exception is

generated as detailed below. There is one special case involving the ILLEGAL opcode (0x4AFC)

;

attempted execution of this instruction always generates an illegal instruction exception, regardless of the

state of the CPUCR[IRD] bit.

The ColdFire variable-length instruction set architecture supports three instruction sizes: 16, 32, or 48 bits.

The first instruction word is known as the operation word (or opword), while the optional words are known

as extension word 1 and extension word 2. The opword is further subdivided into three sections: the upper

four bits segment the entire ISA into 16 instruction lines, the next 6 bits define the operation mode

(opmode), and the low-order 6 bits define the effective address. See Figure 7-11. The opword line

definition is shown in Table 7-10.

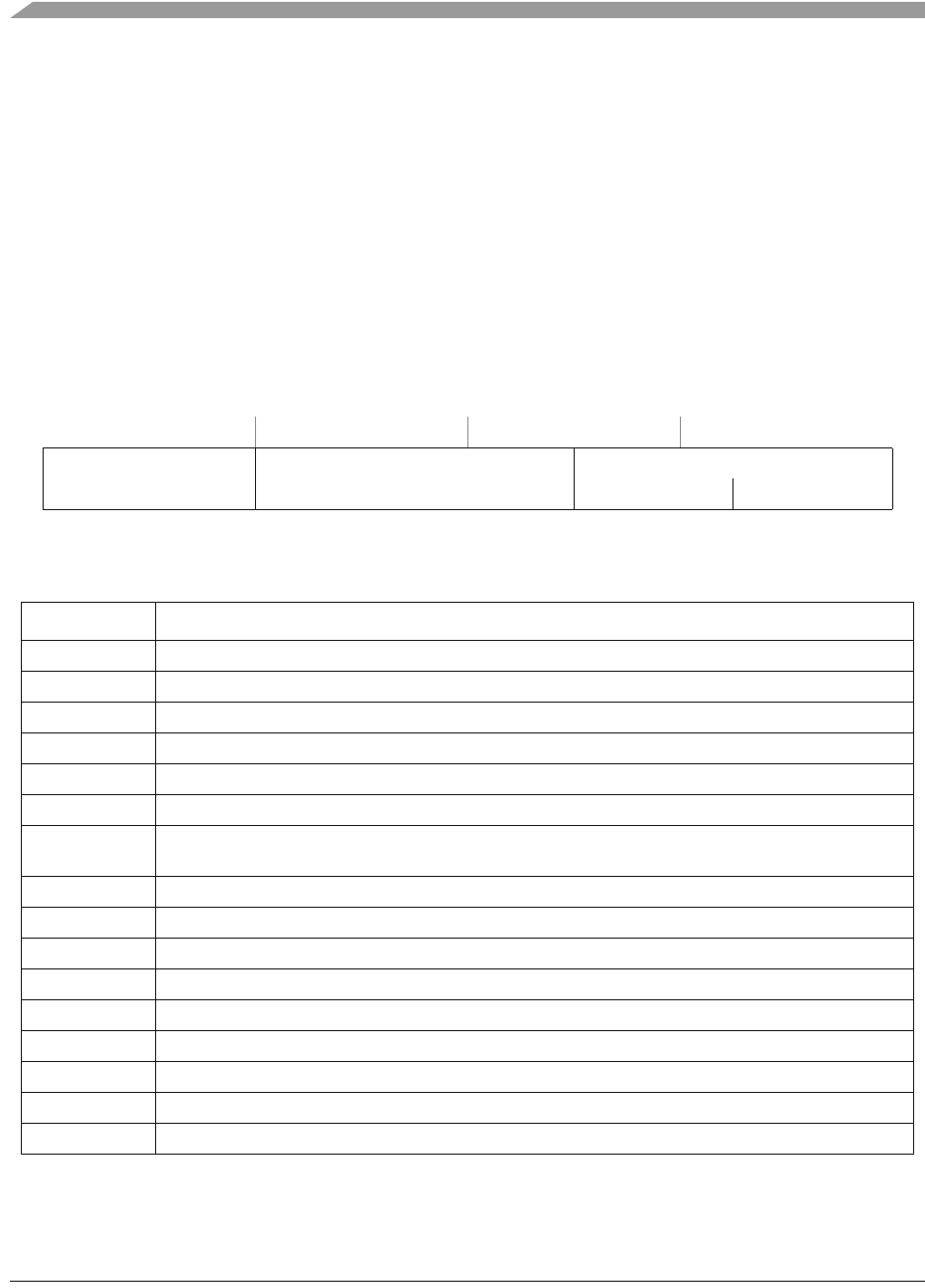

Figure 7-11. ColdFire Instruction Operation Word (Opword) Format

1514131211109876543210

Line OpMode Effective Address

Mode Register

Table 7-10. ColdFire Opword Line Definition

Opword[Line] Instruction Class

0x0 Bit manipulation, Arithmetic and Logical Immediate

0x1 Move Byte

0x2 Move Long

0x3 Move Word

0x4 Miscellaneous

0x5 Add (ADDQ) and Subtract Quick (SUBQ), Set according to Condition Codes (Scc)

0x6 PC-relative change-of-flow instructions

Conditional (Bcc) and unconditional (BRA) branches, subroutine calls (BSR)

0x7 Move Quick (MOVEQ), Move with sign extension (MVS) and zero fill (MVZ)

0x8 Logical OR (OR)

0x9 Subtract (SUB), Subtract Extended (SUBX)

0xA Move 3-bit Quick (MOV3Q)

0xB Compare (CMP), Exclusive-OR (EOR)

0xC Logical AND (AND), Multiply Word (MUL)

0xD Add (ADD), Add Extended (ADDX)

0xE Arithmetic and logical shifts (ASL, ASR, LSL, LSR)

0xF Write DDATA (WDDATA), Write Debug (WDEBUG)