MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 183

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

8.3.2.5 INTC Clear Interrupt Force Register (INTC_CFRC)

The INTC_CFRC register provides a simple memory-mapped mechanism to clear a given bit in the

INTC_FRC register to negate a specific level interrupt request. The data value on the register write causes

the appropriate bit in the INTC_FRC register to be cleared. Attempted reads of this register generate an

error termination.

This register is provided so interrupt service routines can negate a forced interrupt request without the need

to perform a read-modify-write sequence on the INTC_FRC register.

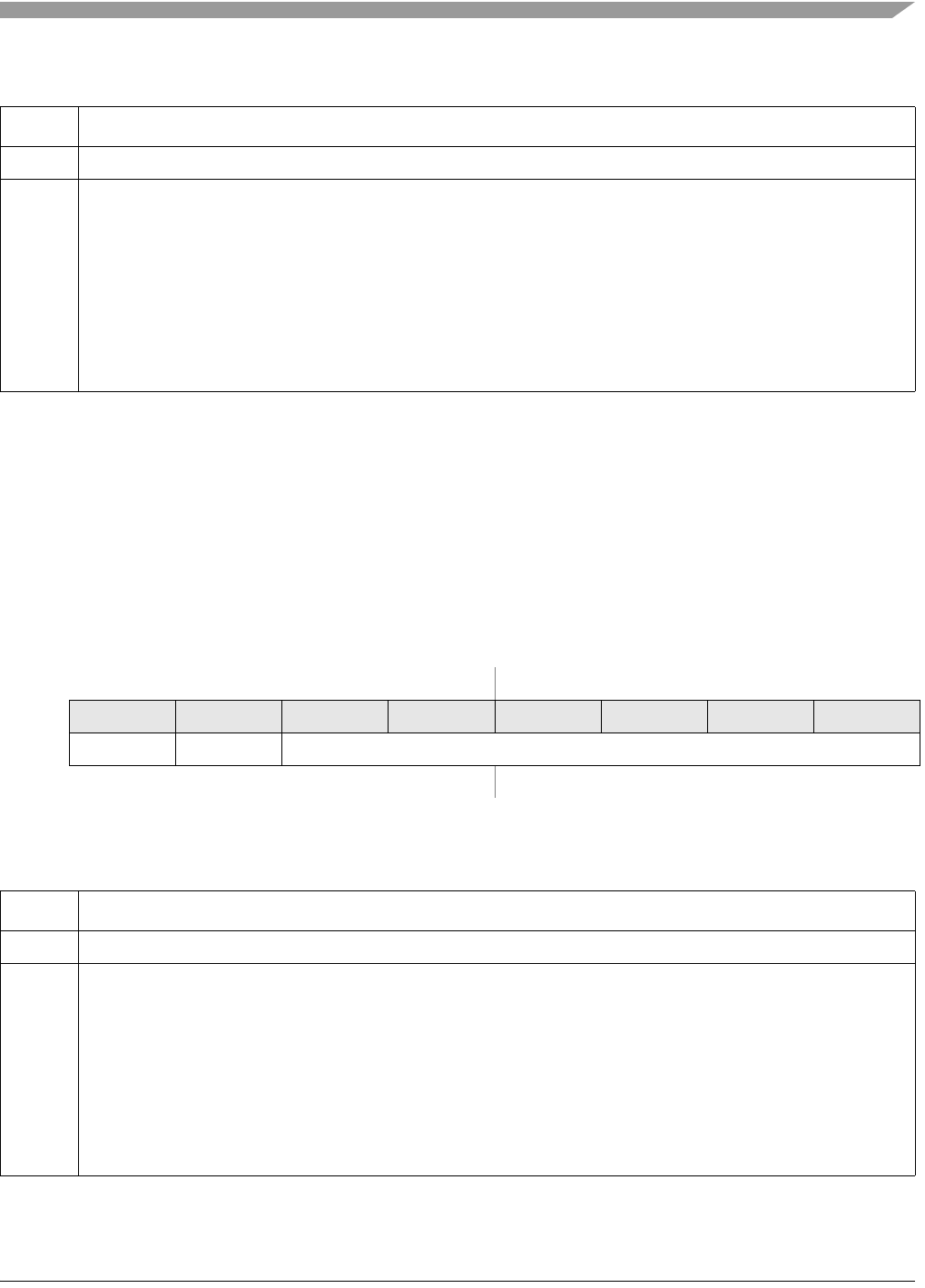

Figure 8-6. INTC_CFRC Register

Table 8-7. INTC_SFRC Field Descriptions

Field Description

7–6 Reserved, must be cleared.

5–0

SET

For data values within the 32–38 range, the corresponding bit in the INTC_FRC register is set, as defined below.

0x20 Bit 32, INTC_FRC[LVL7] is set.

0x21 Bit 33, INTC_FRC[LVL6] is set.

0x22 Bit 34, INTC_FRC[LVL5] is set.

0x23 Bit 35, INTC_FRC[LVL4] is set.

0x24 Bit 36, INTC_FRC[LVL3] is set.

0x25 Bit 37, INTC_FRC[LVL2] is set.

0x26 Bit 38, INTC_FRC[LVL1] is set.

Note: Data values outside this range do not affect the INTC_FRC register. It is recommended the data values be

restricted to the 0x20–0x26 (32–38) range to insure compatibility with future devices.

Offset: CF1_INTC_BASE + 0x1F (INTC_CFRC) Access: Write-only

76543210

R

W0 0 CLR

Reset00000000

Table 8-8. INTC_CFRC Field Descriptions

Field Description

7–6 Reserved, must be cleared.

5–0

CLR

For data values within the 32–38 range, the corresponding bit in the INTC_FRC register is cleared, as defined below.

0x20 Bit 32, INTC_FRC[LVL7] is cleared.

0x21 Bit 33, INTC_FRC[LVL6] is cleared.

0x22 Bit 34, INTC_FRC[LVL5] is cleared.

0x23 Bit 35, INTC_FRC[LVL4] is cleared.

0x24 Bit 36, INTC_FRC[LVL3] is cleared.

0x25 Bit 37, INTC_FRC[LVL2] is cleared.

0x26 Bit 38, INTC_FRC[LVL1] is cleared.

Note: Data values outside this range do not affect the INTC_FRC register. It is recommended the data values be

restricted to the 0x20–0x26 (32–38) range to insure compatibility with future devices.