Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

394 Freescale Semiconductor

Get the latest version from freescale.com

18.4.1.5.4 BACKGROUND

Provided XCSR[ENBDM] is set (BDM enabled), the BACKGROUND command causes the target MCU

to enter active background (halt) mode as soon as the current CPU instruction finishes. If ENBDM is

cleared (its default value), the BACKGROUND command is ignored.

A delay of 16 BDC clock cycles is required after the BACKGROUND command to allow the target MCU

to finish its current CPU instruction and enter active background mode before a new BDC command can

be accepted.

After the target MCU is reset into a normal operating mode, the host debugger would send a

WRITE_XCSR_BYTE command to set ENBDM before attempting to send the BACKGROUND

command the first time. Normally, the development host would set ENBDM once at the beginning of a

debug session or after a target system reset, and then leave the ENBDM bit set during debugging

operations. During debugging, the host would use GO commands to move from active background mode

to normal user program execution and would use BACKGROUND commands or breakpoints to return to

active background mode.

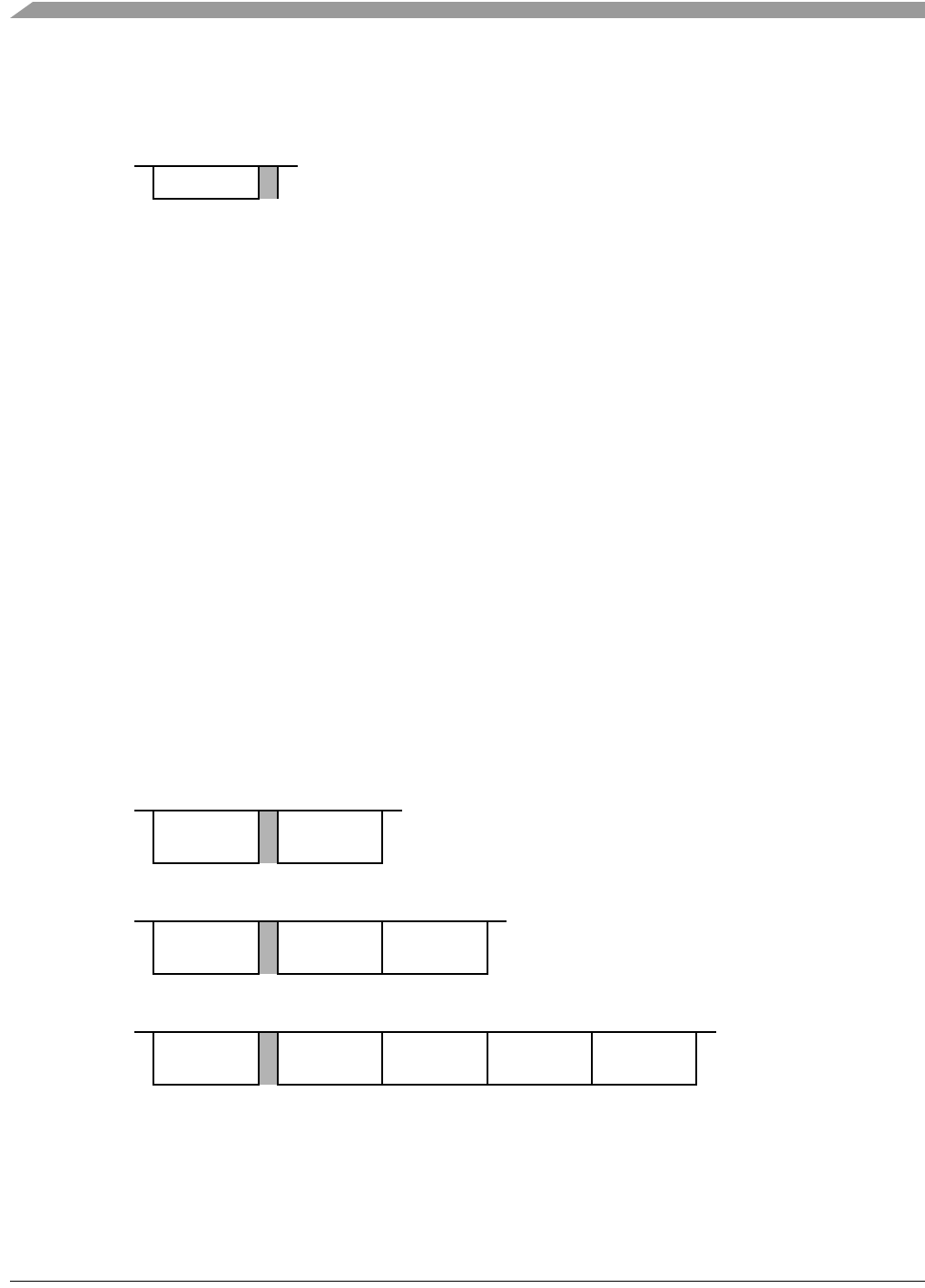

18.4.1.5.5 DUMP_MEM.sz, DUMP_MEM.sz_WS

Enter active background mode (if enabled) Non-intrusive

0x04

host →

target

D

L

Y

DUMP_MEM.sz

Read memory specified by debug address register, then

increment address

Non-intrusive

0x32

Memory

data[7-0]

host →

target

D

L

Y

target →

host

0x36

Memory

data[15-8]

Memory

data[7-0]

host →

target

D

L

Y

target →

host

target →

host

0x3A

Memory

data[31-24]

Memory

data[23-16]

Memory

data[15-8]

Memory

data[7-0]

host →

target

D

L

Y

target →

host

target →

host

target →

host

target →

host