MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 187

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

8.4 Functional Description

The basic operation of the CF1_INTC has been detailed in the preceding sections. This section describes

special rules applicable to non-maskable level seven interrupt requests and the module’s interfaces.

8.4.1 Handling of Non-Maskable Level 7 Interrupt Requests

Level seven interrupts are treated as non-maskable, edge-sensitive requests while levels one through six

are maskable, level-sensitive requests. As a result of this definition, level seven interrupt requests are a

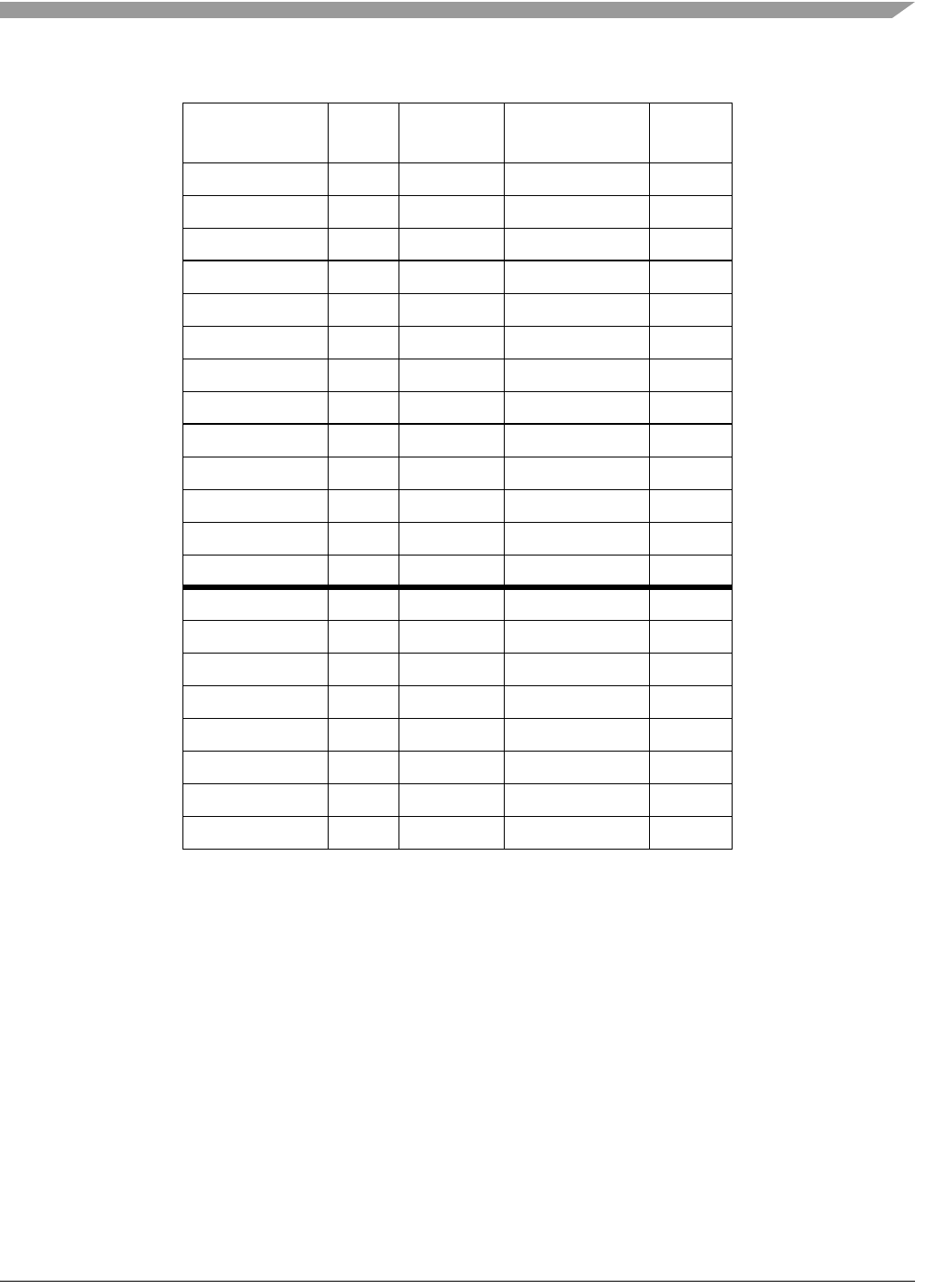

SCI1_rx 4 4 13 77

SCI1_tx 4 3 14 78

force_lvl4 4 0 INTC_FRC[35] 99

IICx

1

3 7 15 79

KBIx

2

3 6 16 80

ADC 3 5 17 81

ACMPx

3

3 4 18 82

force_lvl3 3 0 INTC_FRC[36] 100

SCI2_err 2 5 19 83

SCI2_rx 2 4 20 84

SCI2_tx 2 3 21 85

RTC 2 2 22 86

force_lvl2 2 0 INTC_FRC[37] 101

TPM3_ch0 1 7 23 87

TPM3_ch1 1 6 24 88

TPM3_ch2 1 5 25 89

TPM3_ch3 1 4 26 90

TPM3_ch4 1 3 27 91

TPM3_ch5 1 2 28 92

TPM3_ovfl 1 1 29 93

force_lvl1 1 0 INTC_FRC[38] 102

1

There are two I

2

C modules on-chip. They share a common interrupt vector.

2

The keyboard features are available on GPIO ports B and D. The two

modules share a common interrupt vector.

3

There are two analog comparator modules on-chip. They share a common

interrupt vector.

Table 8-12. V1 ColdFire Interrupt Assignments (continued)

IRQ Source Level

Priority

within Level

Interrupt Source

Number

Vector