Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 387

Get the latest version from freescale.com

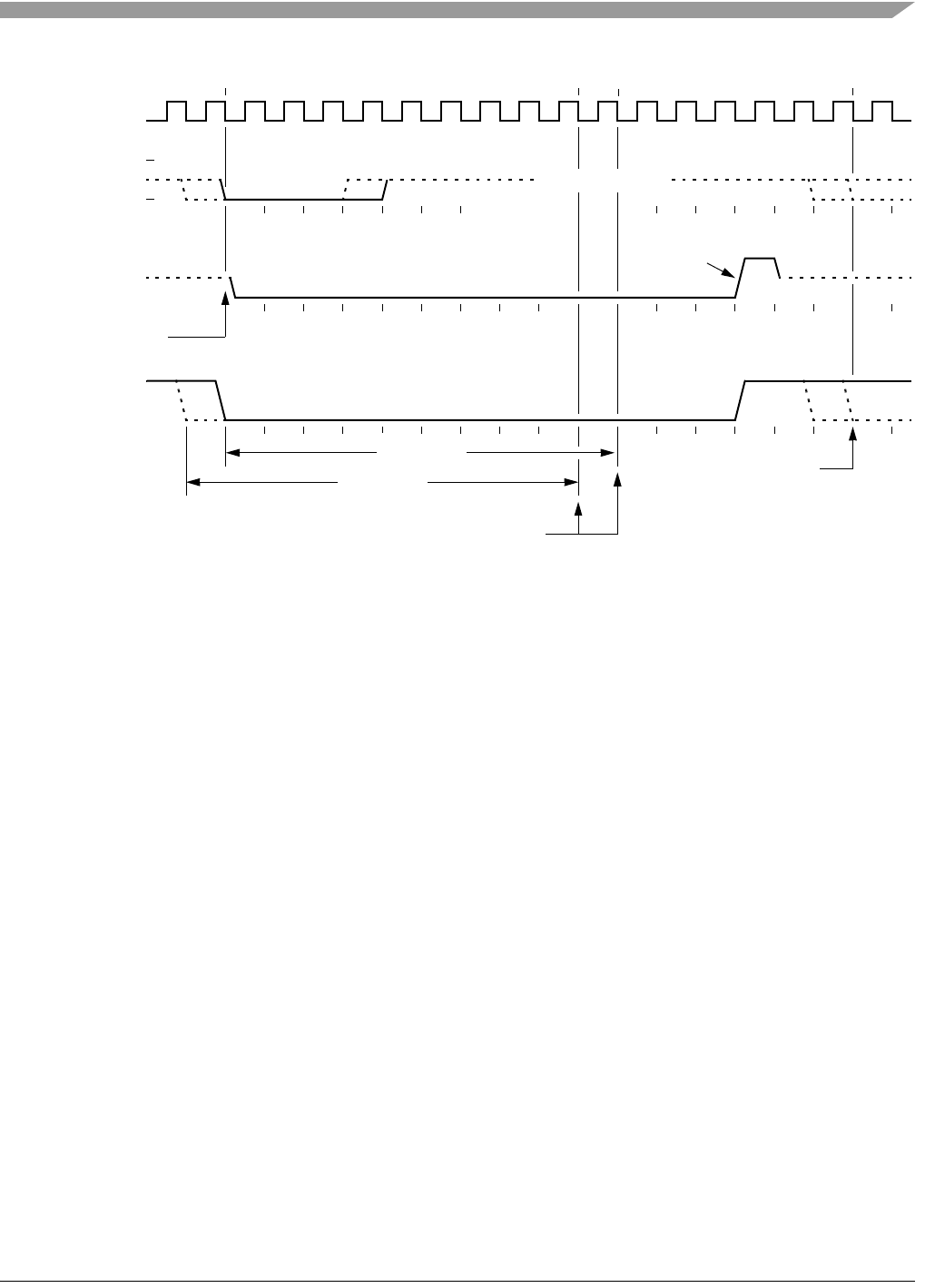

Figure 18-17. BDM Target-to-Host Serial Bit Timing (Logic 0)

18.4.1.4 BDM Command Set Descriptions

This section presents detailed descriptions of the BDM commands.

The V1 BDM command set is based on transmission of one or more 8-bit data packets per operation. Each

operation begins with a host-to-target transmission of an 8-bit command code packet. The command code

definition broadly maps the operations into four formats as shown in Figure 18-18.

10 CYCLES

BDC CLOCK

(TARGET MCU)

HOST DRIVE

TO BKGD PIN

TARGET MCU

DRIVE AND

PERCEIVED START

OF BIT TIME

HIGH-IMPEDANCE

BKGD PIN

10 CYCLES

SPEED-UP PULSE

SPEEDUP

PULSE

EARLIEST START

OF NEXT BIT

HOST SAMPLES BKGD PIN