MCF51QE128 MCU Series Reference Manual, Rev. 3

92 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 4 Memory

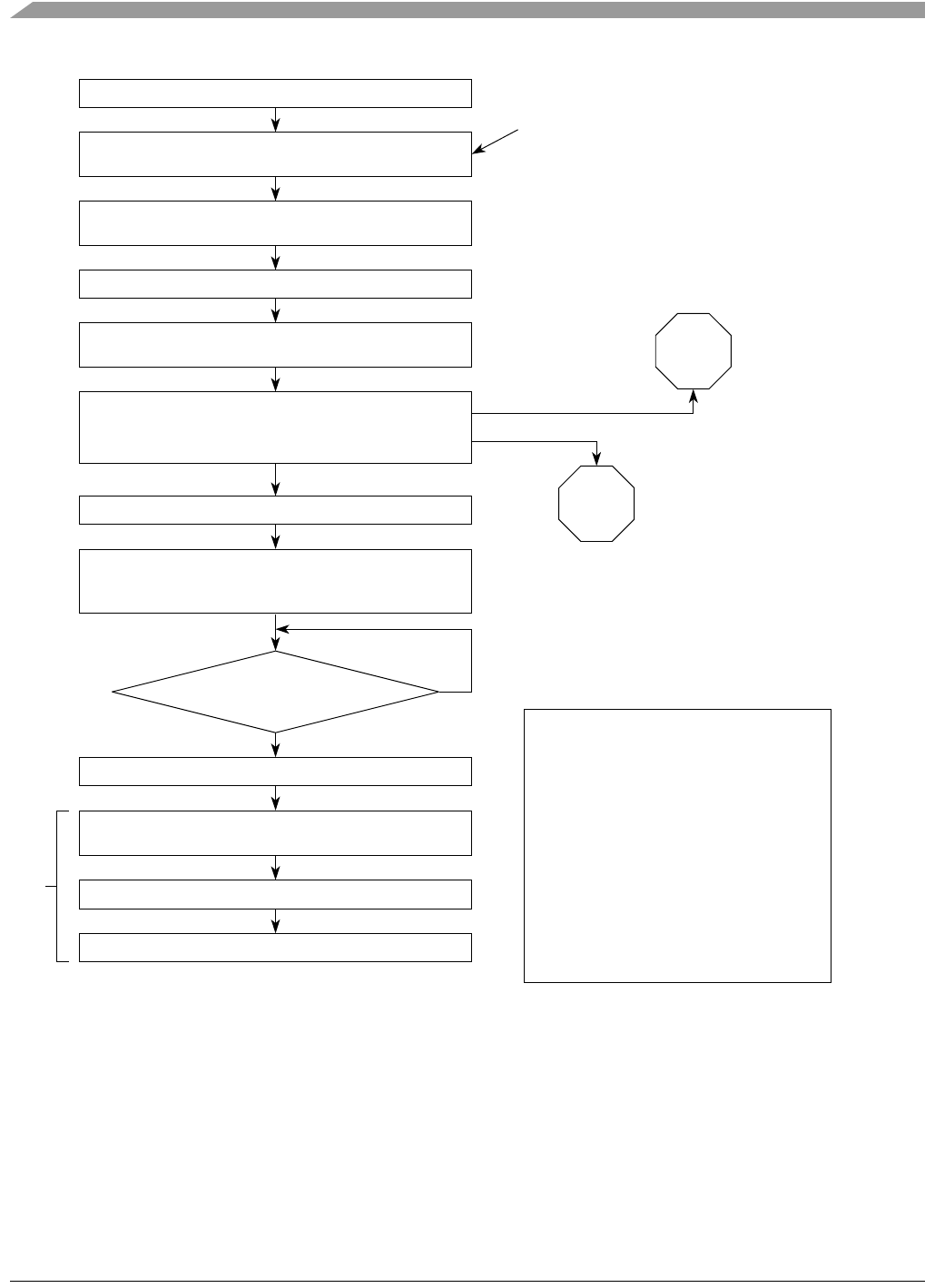

Figure 4-15. Procedure for Clearing Security on MCF51QE128/64/32 via the BDM Port

Write CSR2[25:24]=11 to initiate BDM reset to halt or

write CSR2[25:24]=01 to initiate BDM reset to run

On-chip flash is erased and unsecure

Is XCSR[25] cleared

(erase/verify complete)

?

Ye s

No

Write XCSR[31:24] = 0x87 to initiate

erase/verify of flash memory

Set PRDIV8 and clock divider fields in CSR3

Delay ‘TBD’ cycles

Device is unsecure

1

1. The last three steps are optional, but recommended.

Ways to enter BDM halt mode:

1. BKGD=0 during POR

BKGD=0 during external reset

BKGD=0 during BDM reset

BFHBR=1 during BDM reset

Issue BACKGROUND command

via BDM interface

HALT instruction

BDM breakpoint

ColdFire fault-on-fault

Of these, only method 1 is guaranteed to work under

all circumstances because of the ability to program

2.

3.

4.

5.

6.

7.

8.

XCSR[31:24] = 0x87

N = number of cycles for SIM to release internal

reset. Adder of 16 imposed by ColdFire core.

STOP

XCSR[25] = 0

STOP

Secure state unknown, CPU halted,

FEI 10 MHz clock, synchronized to debugger

SYNC

Secure state unknown, CPU halted,

FEI 10 MHz clock, SYNC required

Hold BKGD=0, apply power, wait N+16 cycles

for POR to deassert

Secure state unknown/unpowered

BKGD=0 during reset ensures that

ENBDM comes up ‘1’.

FLL enabled, internal reference (FEI)

at 10MHz is reset default for the ICS.

Error condition

check code or device.

Already

XCSR[31:24] ≠ 1000_01x1

Read XCSR

unsecured

Note: This write is required

different functions on the BKGD package pin.