MCF51QE128 MCU Series Reference Manual, Rev. 3

124 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 6 Parallel Input/Output Control

6.7.3.2 Port C Data Direction Register (PTCDD)

6.7.3.3 Port C Data Set Register (PTCSET)

6.7.3.4 Port C Data Clear Register (PTCCLR)

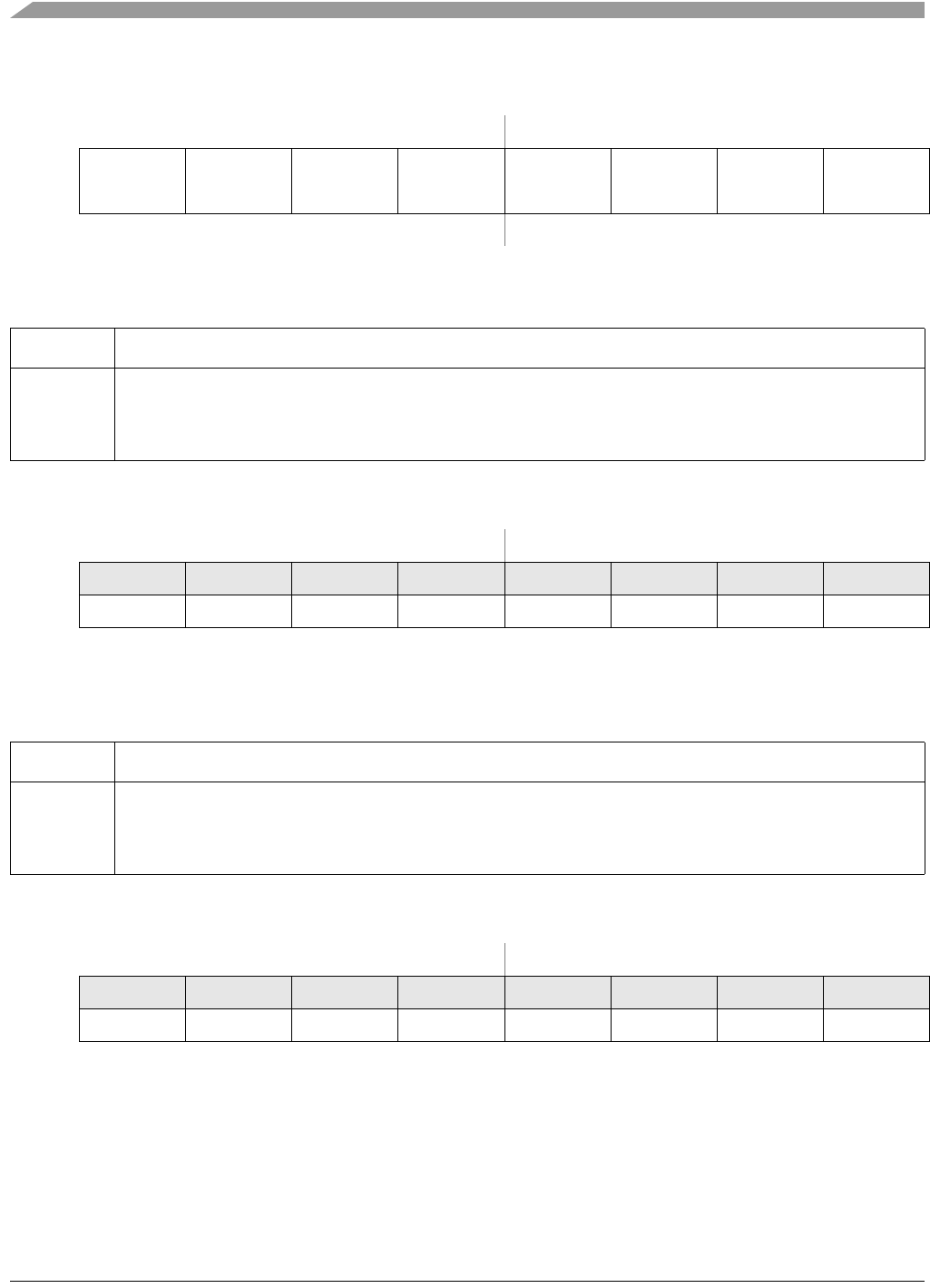

76543210

R

PTCDD7 PTCDD6 PTCDD5 PTCDD4 PTCDD3 PTCDD2 PTCDD1 PTCDD0

W

Reset:00000000

Figure 6-15. Port C Data Direction Register (PTCDD)

Table 6-12. PTCDD Register Field Descriptions

Field Description

7–0

PTCDDn

Data Direction for Port C Bits. These read/write bits control the direction of port C pins and what is read for PTCD

reads.

0 Input (output driver disabled) and reads return the pin value.

1 Output driver enabled for port C bit n and PTCD reads return the contents of PTCDn.

76543210

R

W PTCSET7 PTCSET6 PTCSET5 PTCSET4 PTCSET3 PTCSET2 PTCSET1 PTCSET0

Reset:00000000

Figure 6-16. Port C Data Set Register (PTCSET)

Table 6-13. PTCSET Register Field Descriptions

Field Description

7–0

PTCSETn

Data Set for Port C Bits. Writing 1 to any bit in this location sets the corresponding bit in the data register. Writing

a zero to any bit in this register has no effect.

0 Corresponding PTCDn maintains current value.

1 Corresponding PTCDn is set.

76543210

R

W PTCCLR7 PTCCLR6 PTCCLR5 PTCCLR4 PTCCLR3 PTCCLR2 PTCCLR1 PTCCLR0

Reset:00000000

Figure 6-17. Port C Data Clear Register (PTCCLR)