Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

382 Freescale Semiconductor

Get the latest version from freescale.com

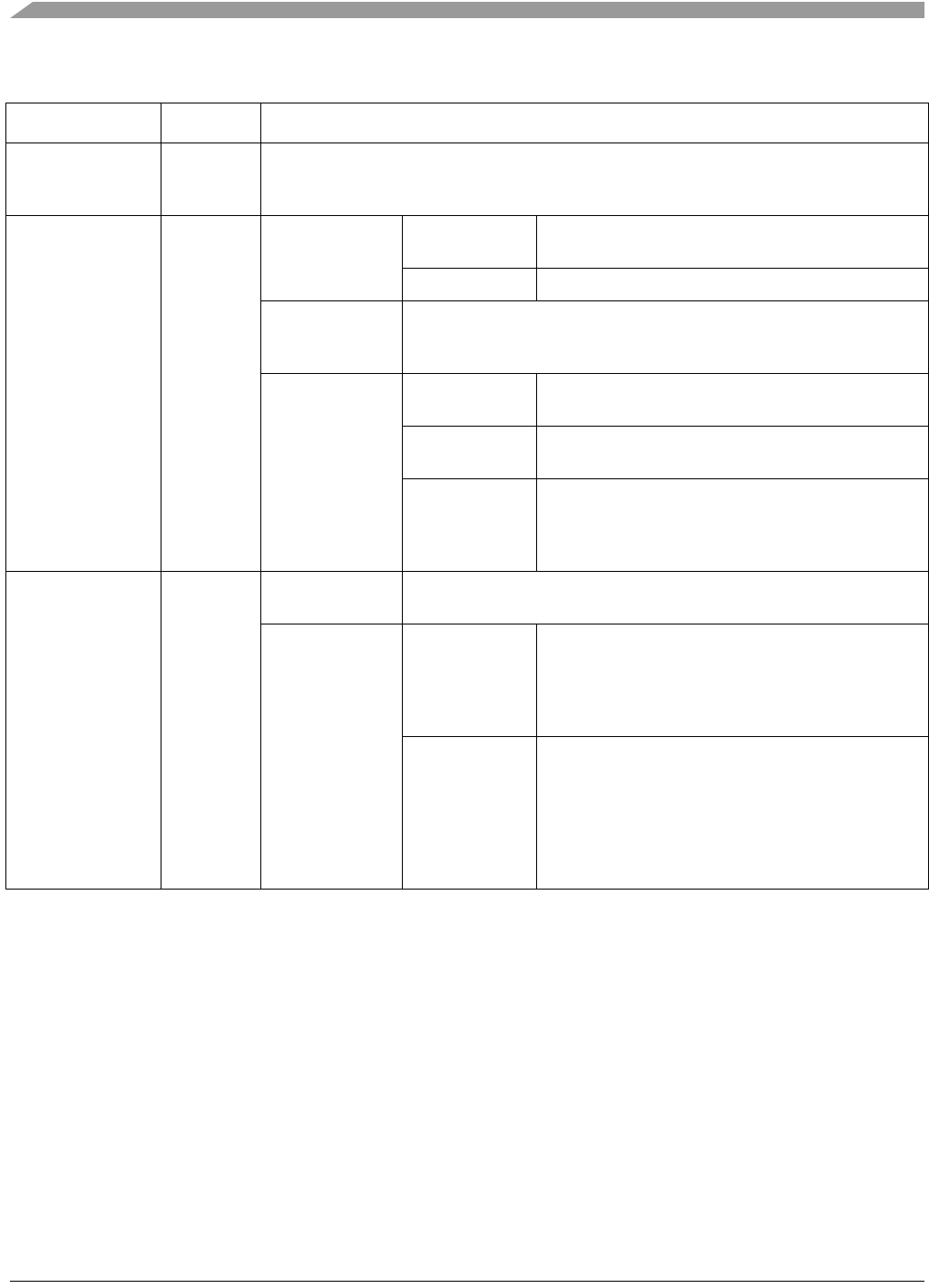

Hardware

breakpoint trigger

Pending

Halt is made pending in the processor. The processor samples for pending halt and interrupt

conditions once per instruction. When a pending condition is asserted, the processor halts

execution at the next sample point.

HALT instruction Immediate

BDM disabled

CPUCR[IRD] = 0

A reset is initiated since attempted execution of an

illegal instruction

CPUCR[IRD] = 1 An illegal instruction exception is generated.

BDM enabled,

supervisor mode

Processor immediately halts execution at the next instruction sample

point. The processor can be restarted by a BDM GO command.

Execution continues at the instruction after HALT.

BDM enabled,

user mode

CSR[UHE] = 0

CPUCR[IRD] = 0

A reset event is initiated, since a privileged instruction

was attempted in user mode.

CSR[UHE] = 0

CPUCR[IRD] = 1

A privilege violation exception is generated.

CSR[UHE] = 1

Processor immediately halts execution at the next

instruction sample point. The processor can be

restarted by a BDM GO command. Execution

continues at the instruction after HALT.

BACKGROUND

command

Pending

BDM disabled or

flash secure

Illegal command response and BACKGROUND command is ignored.

BDM enabled and

flash unsecure

Processor is

running

Halt is made pending in the processor. The processor

samples for pending halt and interrupt conditions

once per instruction. When a pending condition is

asserted, the processor halts execution at the next

sample point.

Processor is

stopped

Processing of the BACKGROUND command is

treated in a special manner. The processor exits the

stopped mode and enters the halted state, at which

point all BDM commands may be exercised. When

restarted, the processor continues by executing the

next sequential instruction (the instruction following

STOP).

Table 18-23. CPU Halt Sources (continued)

Halt Source Halt Timing Description