Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

392 Freescale Semiconductor

Get the latest version from freescale.com

18.4.1.5.1 SYNC

The SYNC command is unlike other BDC commands because the host does not necessarily know the

correct speed to use for serial communications until after it has analyzed the response to the SYNC

command.

To issue a SYNC command, the host:

1. Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (bus clock or

device-specific alternate clock source).

2. Drives BKGD high for a brief speed-up pulse to get a fast rise time. (This speedup pulse is typically

one cycle of the host clock which is as fast as the maximum target BDC clock.)

3. Removes all drive to the BKGD pin so it reverts to high impedance.

4. Listens to the BKGD pin for the sync response pulse.

Upon detecting the sync request from the host (which is a much longer low time than would ever occur

during normal BDC communications), the target:

1. Waits for BKGD to return to a logic high.

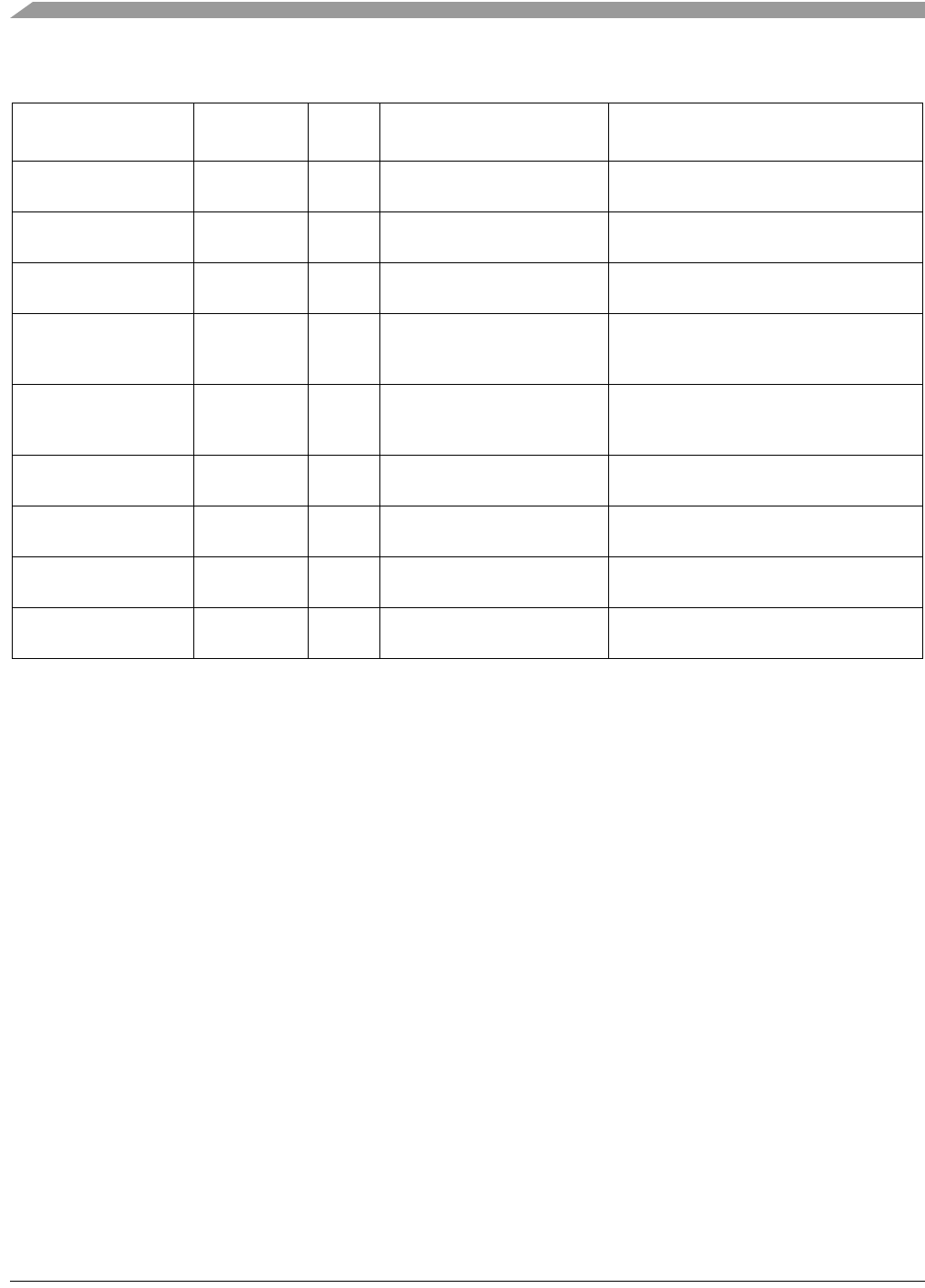

SYNC_PC Non-Intrusive Yes 0x01/d Display the CPU’s current PC and capture

it in the PST trace buffer

WRITE_CREG Active

Background

Yes (0xC0+CRN)/wd32/d Write one of the CPU’s control registers

WRITE_DREG Non-Intrusive Yes (0x80+CRN)/wd32/d Write one of the debug module’s control

registers

WRITE_MEM.sz Non-Intrusive Yes (0x10+4 x sz)/ad24/wd.sz/d Write the appropriately-sized (sz) memory

value to the location specified by the 24-bit

address

WRITE_MEM.sz_WS Non-Intrusive No (0x11+4 x sz)/ad24/wd.sz/d/ss Write the appropriately-sized (sz) memory

value to the location specified by the 24-bit

address and report status

WRITE_Rn Active

Background

Yes (0x40+CRN)/wd32/d Write the requested general-purpose

register (An, Dn) of the CPU

WRITE_XCSR_BYTE Always

Available

No 0x0D/wd8 Write the most significant byte of the debug

module’s XCSR

WRITE_CSR2_BYTE Always

Available

No 0x0E/wd8 Write the most significant byte of the debug

module’s CSR2

WRITE_CSR3_BYTE Always

Available

No 0x0F/wd8 Write the most significant byte of the debug

module’s CSR3

1

This column identifies if the command generates an ACK pulse if operating with acknowledge mode enabled. See

Section 18.4.1.7, “Hardware Handshake Abort Procedure,” for addition information.

2

The SYNC command is a special operation which does not have a command code.

3

If a GO command is received while the processor is not halted, it performs no operation.

Table 18-25. BDM Command Summary (continued)

Command

Mnemonic

Command

Classification

ACK

if Enb?

1

Command

Structure

Description