Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

358 Freescale Semiconductor

Get the latest version from freescale.com

When operating in secure mode, as defined by a 2-bit field in the flash memory examined at reset, BDM

access to debug resources is extremely restricted. It is possible to tell that the device has been secured, and

to clear security, which involves mass erasing the on-chip flash memory. No other debug access is allowed.

Secure mode can be used in conjunction with each of the wait and stop low-power modes.

If the BDM interface is not enabled, access to the debug resources is limited in the same manner as a secure

device.

If the device is not secure and the BDM interface is enabled (XCSR[ENBDM] is set), the device is

operating in debug mode and additional resources are available via the BDM interface. In this mode, the

mode of the processor (running, stopped, or halted) determines which BDM commands may be used.

Debug mode functions are managed through the background debug controller (BDC) in the Version 1

ColdFire core. The BDC provides the means for analyzing MCU operation during software development.

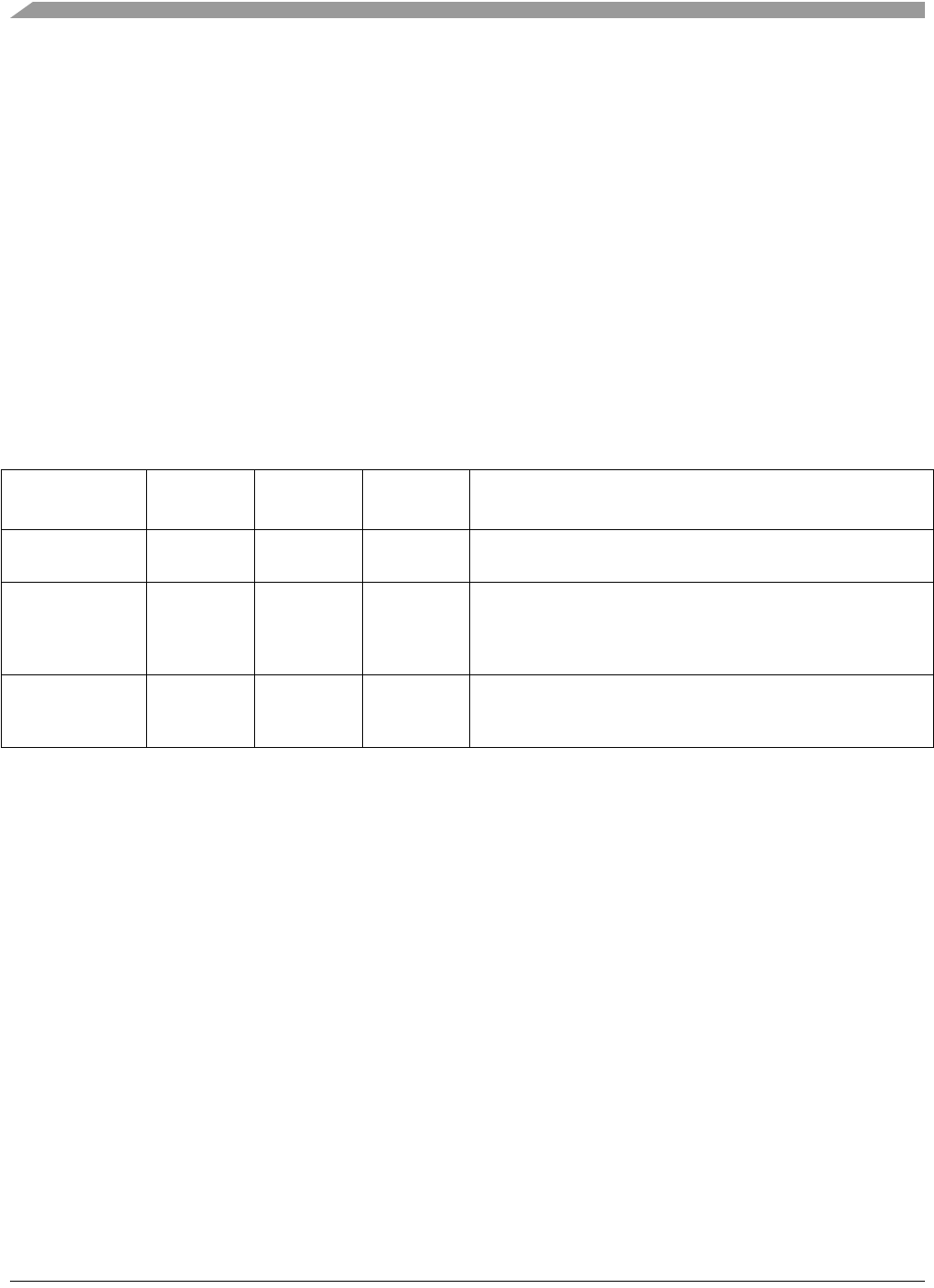

BDM commands can be classified into three types as shown in Table 18-2.

For more information on these three BDM command classifications, see Section 18.4.1.5, “BDM

Command Set Summary.”

The core’s halt mode is entered in a number of ways:

• The BKGD pin is low during POR.

• The BKGD pin is low immediately after a BDM-initiated force reset (see Section 18.3.3,

“Configuration/Status Register 2 (CSR2),” for details).

• A background debug force reset occurs (CSR2[BDFR] is set) and CSR2[BFHBR] is set.

• A BACKGROUND command is received through the BKGD pin. If necessary, this wakes the

device from STOP/WAIT modes.

• A properly-enabled (XCSR[ENBDM] is set) HALT instruction is executed.

• Encountering a BDM breakpoint and the trigger response is programmed to generate a halt

While in halt mode, the core waits for serial background commands rather than executing instructions from

the application program.

Table 18-2. BDM Command Types

Command Type

Flash

Secure?

BDM? Core Status Command Set

Always-available

Secure or

Unsecure

Enabled or

Disabled

—

• Read/write access to XCSR[31–24], CSR2[31–24],

CSR3[31–24]

Non-intrusive Unsecure Enabled Run, Halt

• Memory access

• Memory access with status

• Debug register access

• BACKGROUND

Active background Unsecure Enabled Halt

• Read or write CPU registers (also available in stop mode)

• Single-step the application

• Exit halt mode to return to the application program (GO)