ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

166 Freescale Semiconductor

Information loaded into D1 defines the local memory hardware configuration as shown in the figure below.

BDM: Load: 0x61 (D1)

Store: 0x41 (D1)

Access: User read-only

BDM read-only

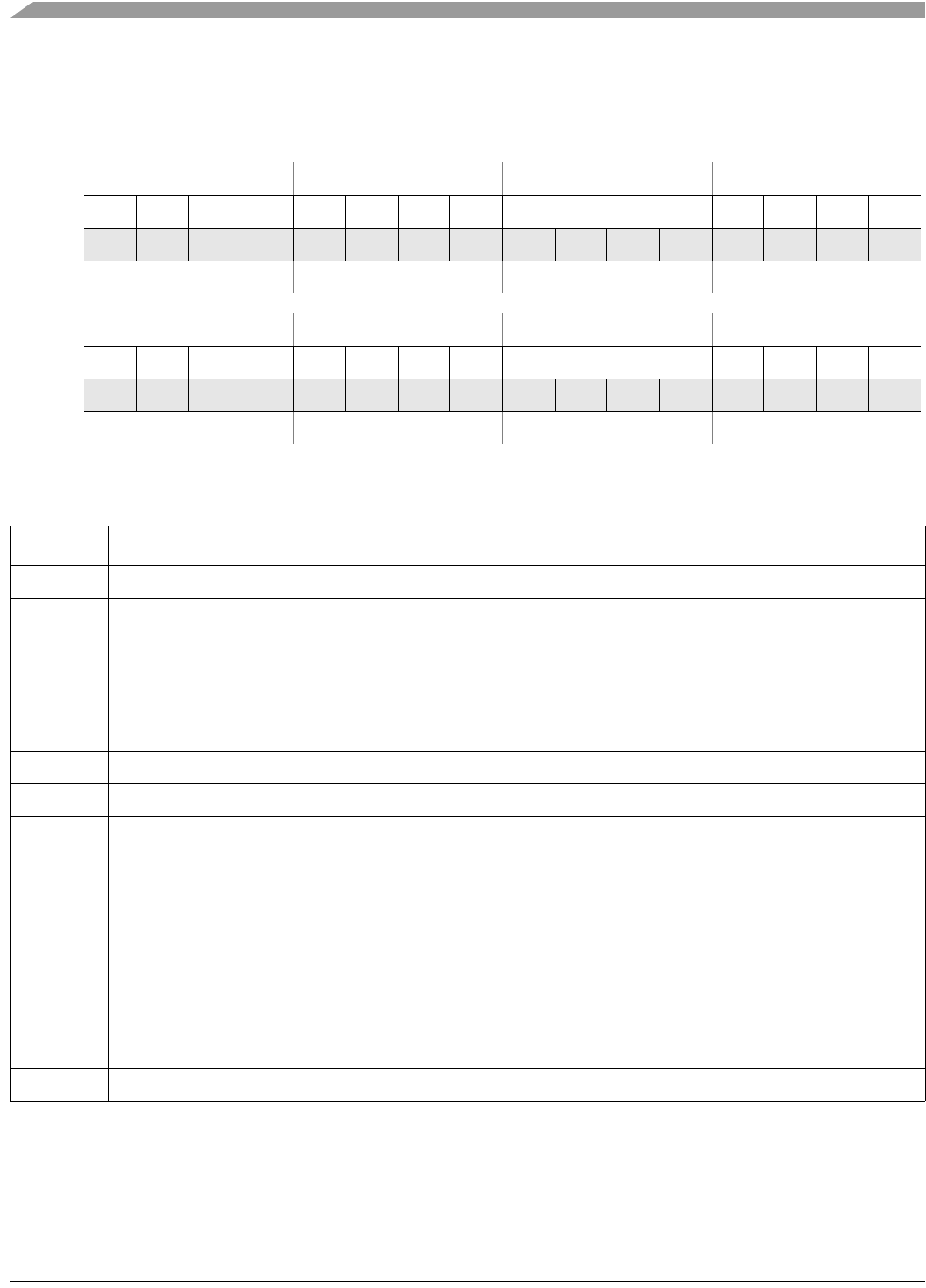

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R00010000 FLASHSZ 0000

W

Reset0001000010010000

1514131211109876543210

R00000000 SRAMSZ 0000

W

Reset0000000001010000

Figure 7-13. D1 Hardware Configuration Info

Table 7-12. D1 Hardware Configuration Information Field Description

Field Description

31–24 Reserved.

23–20

FLASHSZ

Flash bank size.

0000-0111 No flash

1000 64-Kbyte flash

1001 128-Kbyte flash

1010 256-Kbyte flash

1011 512-Kbyte flash

Else Reserved for future use.

19–16 Reserved

15–8 Reserved

7–4

SRAMSZ

SRAM bank size.

0000 No SRAM

0001 512 bytes

0010 1 Kbytes

0011 2 Kbytes

0100 4 Kbytes

0101 8 Kbytes (This is the value used for this device)

0110 16 Kbytes

0111 32 Kbytes

1000 64 Kbytes

1001 128 Kbytes

Else Reserved for future use

3-0 Reserved.