MCF51QE128 MCU Series Reference Manual, Rev. 3

180 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

NOTE

Take special notice of the bit numbers within this register, 39–32. This is for

compatibility with previous ColdFire interrupt controllers.

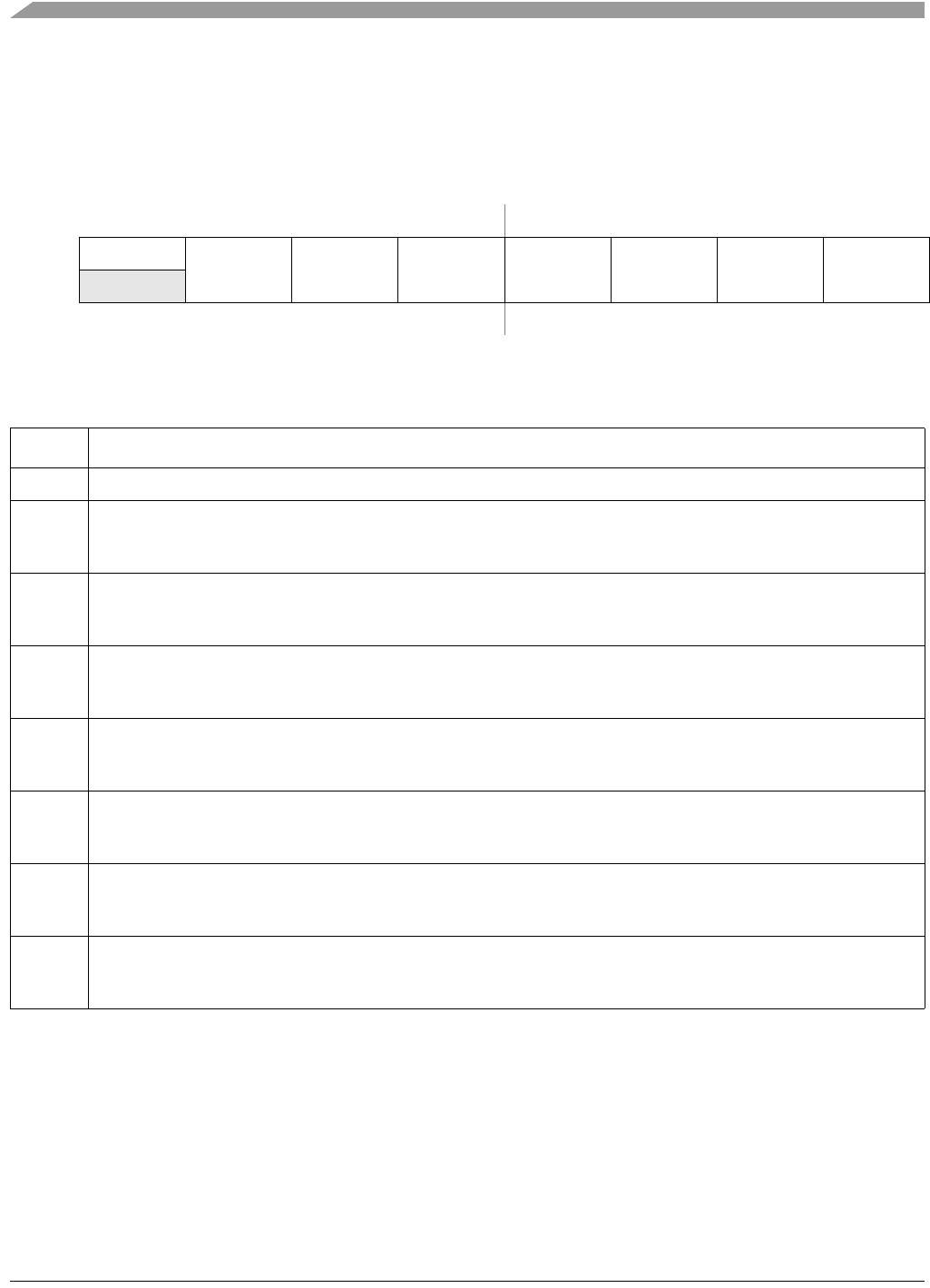

Figure 8-2. INTC_FRC Register

8.3.2.2 INTC Programmable Level 6, Priority {7,6} Registers (INTC_PL6P{7,6})

The two level seven interrupt requests (the IRQ package pin and the low-voltage detection interrupt)

cannot have their levels reassigned. However, any of the remaining peripheral interrupt requests can be

reassigned as the highest priority maskable requests using these two registers. The vector number

associated with the interrupt requests is not changed. Rather, only the interrupt request's level and priority

are altered, based on the contents of the INTC_PL6P{7,6} registers.

Offset: CF1_INTC_BASE + 0x13 (INTC_FRC) Access: Read/Write

39 38 37 36 35 34 33 32

R 0

LVL1 LVL2 LVL3 LVL4 LVL5 LVL6 LVL7

W

Reset00000000

Table 8-4. INTC_FRC Field Descriptions

Field Description

39 Reserved, must be cleared.

38

LVL1

Force Level 1 interrupt.

0 Negates the forced level 1 interrupt request.

1 Forces a level 1 interrupt request.

37

LVL2

Force Level 2 interrupt.

0 Negates the forced level 2 interrupt request.

1 Forces a level 2 interrupt request.

36

LVL3

Force Level 3 interrupt.

0 Negates the forced level 3 interrupt request.

1 Forces a level 3 interrupt request.

35

LVL4

Force Level 4 interrupt.

0 Negates the forced level 4 interrupt request.

1 Forces a level 4 interrupt request.

34

LVL5

Force Level 5 interrupt.

0 Negates the forced level 5 interrupt request.

1 Forces a level 5 interrupt request.

33

LVL6

Force Level 6 interrupt.

0 Negates the forced level 6 interrupt request.

1 Forces a level 6 interrupt request.

32

LVL7

Force Level 7 interrupt.

0 Negates the forced level 7 interrupt request.

1 Forces a level 7 interrupt request.