MCF51QE128 MCU Series Reference Manual, Rev. 3

86 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 4 Memory

4.5.2.5 Mass Erase Command

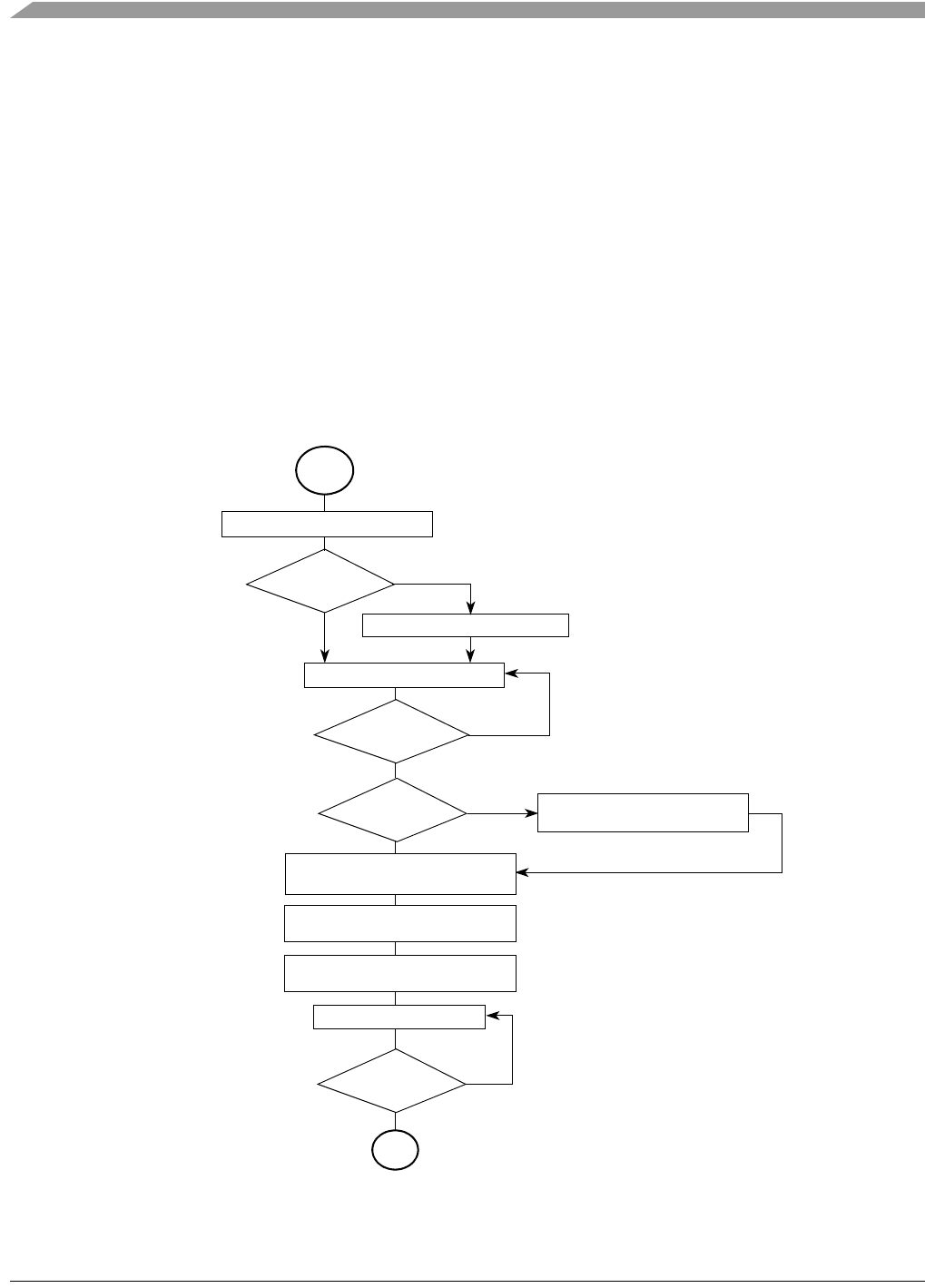

The mass erase operation erases the entire flash array memory using an embedded algorithm. An example

flow to execute the mass erase operation is shown in Figure 4-14. The mass erase command write sequence

is as follows:

1. Write to an aligned flash block address to start the command write sequence for the mass erase

command. The address and data written is ignored.

2. Write the mass erase command, 0x41, to the FCMD register.

3. Clear the FCBEF flag in the FSTAT register by writing a 1 to FCBEF to launch the mass erase

command.

If the flash array memory to be mass erased contains any protected area, FSTAT[FPVIOL] is set and the

mass erase command does not launch. After the mass erase command has successfully launched and the

mass erase operation has completed, FSTAT[FCCF] is set.

Figure 4-14. Example Mass Erase Command Flow

Write: Flash Memory Address

Write: FCMD register

Write: FSTAT register

1.

2.

3.

Write: FSTAT register

yes

no

Access Error and

no

Bit Polling for

Read: FSTAT register

yes

Read: FSTAT register

no

START

yes

FCBEF

Set?

Command

FCCF

Set?

FACCERR/FPVIOL

Set?

Write: FCDIV register

Read: FCDIV register

yes

no

Clock Register

FDIVLD

Set?

Note: FCDIV needs to

Written

Check

Protection Violation

Check

Buffer Empty Check

and Dummy Data

Mass Erase Command 0x41

Clear FCBEF 0x80

Clear FACCERR/FPVIOL 0x30

Command Completion

Check

EXIT

be set after each reset