MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 177

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

means the 30 sources are mapped to a sparsely-populated two-dimensional ColdFire array of seven

interrupt levels and nine priorities within the level. The following association between the HCS08 and

ColdFire vector numbers applies:

ColdFire Vector Number = 62 + HCS08 Vector Number

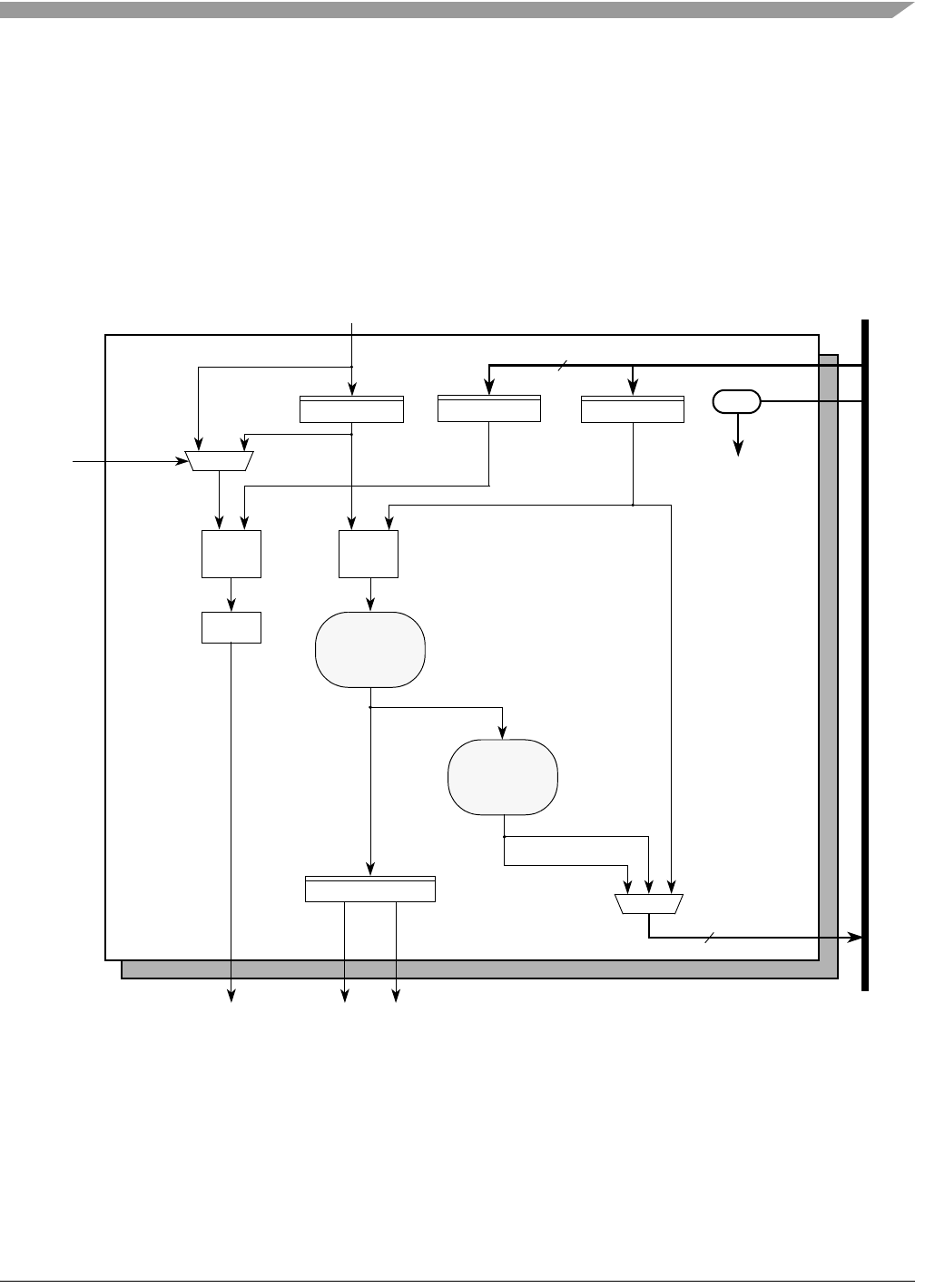

The CF1_INTC performs a cycle-by-cycle evaluation of the active requests and signals the highest-level,

highest-priority request to the V1 ColdFire core in the form of an encoded interrupt level and the exception

vector associated with the request. The module also includes a byte-wide interface to access its

programming model. These interfaces are shown in the simplified block diagram of Figure 8-1.

Figure 8-1. CF1_INTC Block Diagram

8.1.2 Features

The Version 1 ColdFire interrupt controller includes:

CF1_INTC

INTC_FRC

INTC_WCR

ipr

decode

≥>

IACK

Vector Mux

Prioritization

Vector Gen

8

8

&

mux

≥

mux

data to module

address

Peripheral Bus

Interrupt Source Number

data from module

Wake-up Interrupt Level & Vector

to V1 ColdFire core

Enable Wake-up

Spurious Vector

Level n Vector