Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

356 Freescale Semiconductor

Get the latest version from freescale.com

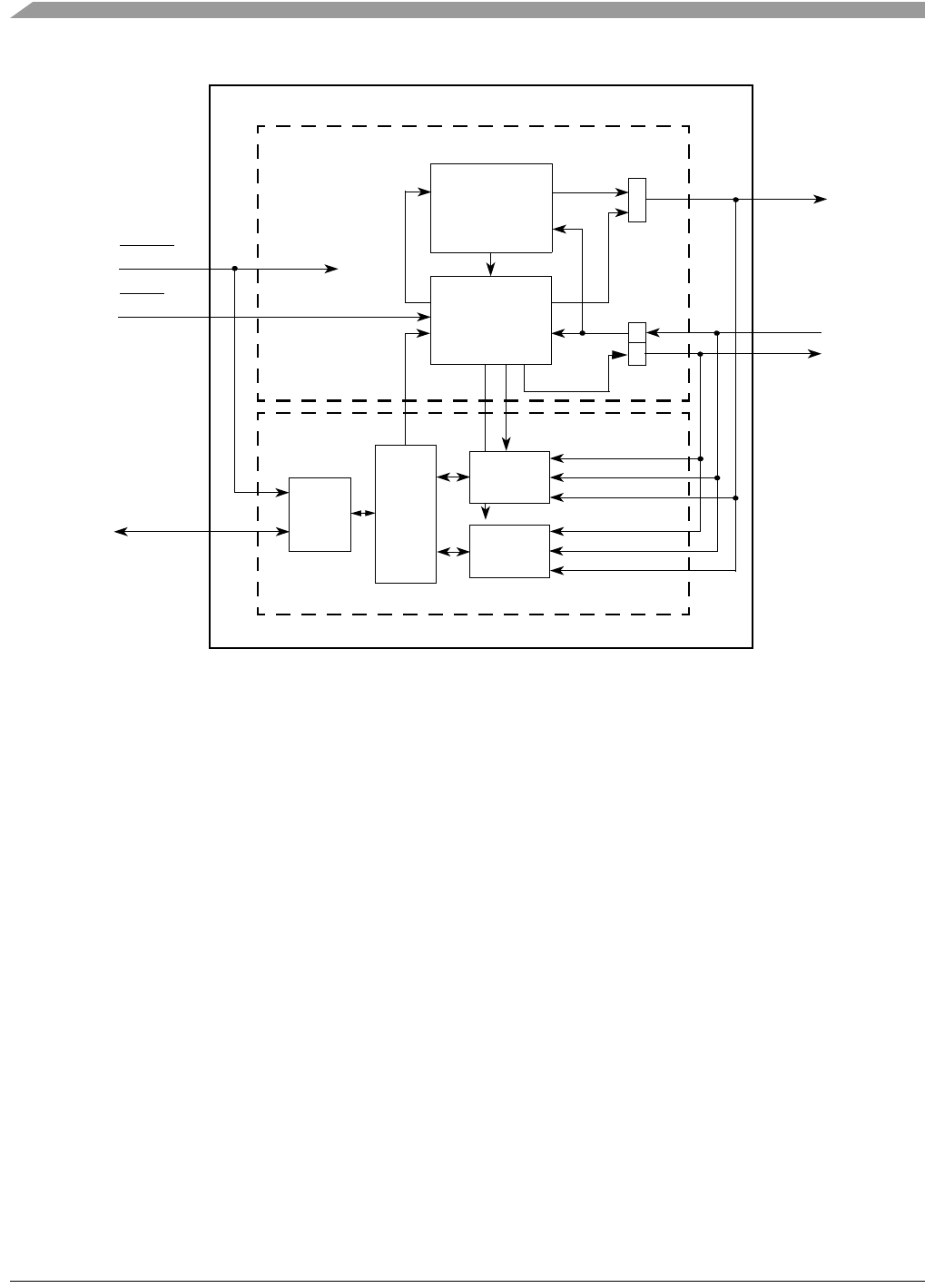

Figure 18-1. Simplified Version 1 ColdFire Core Block Diagram

18.1.1 Overview

Debug support is divided into three areas:

• Background debug mode (BDM)—Provides low-level debugging in the ColdFire processor core.

In BDM, the processor core is halted and a variety of commands can be sent to the processor to

access memory, registers, and peripherals. The external emulator uses a one-pin serial

communication protocol. See Section 18.4.1, “Background Debug Mode (BDM)”.

• Real-time debug support—Use of the full BDM command set requires the processor to be halted,

which many real-time embedded applications cannot support. The core includes a variety of

internal breakpoint registers which can be configured to trigger and generate a special interrupt.

The resulting debug interrupts let real-time systems execute a unique service routine that can

quickly save the contents of key registers and variables and return the system to normal operation.

The external development system can then access the saved data, because the hardware supports

Central Processing Unit

Debug

Version 1 ColdFire Core (CF1Core)

IFP

OEP

BDC

CFx

BDM

PST/

DDATA

RTD

addr

rdata

wdata

BKGD

RESET

IPL_B[2:0]

IFP — Instruction fetch pipeline

OEP — Operand execution pipeline

BDC — Background debug controller

CFxBDM — ColdFire background debug module

PST/DDATA — Processor status/debug data

RTD — Real-time debug

(CF1Cpu)

(CF1Dbg)