MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 107

Get the latest version from freescale.com

Chapter 5 Resets, Interrupts, and General System Control

5.7.9 System Clock Gating Control 1 Register (SCGC1)

This high page register contains control bits to enable or disable the bus clock to the TPMx, ADC, IICx,

and SCIx modules. Gating off the clocks to unused peripherals reduces the MCU’s run and wait currents.

See Section 5.6, “Peripheral Clock Gating,” for more information.

5.7.10 System Clock Gating Control 2 Register (SCGC2)

This high page register contains control bits to enable or disable the bus clock to the IRQ, KBI, ACMP,

RTC, and SPIx modules. Gating off the clocks to unused peripherals reduces the MCU’s run and wait

currents. See Section 5.6, “Peripheral Clock Gating,” for more information.

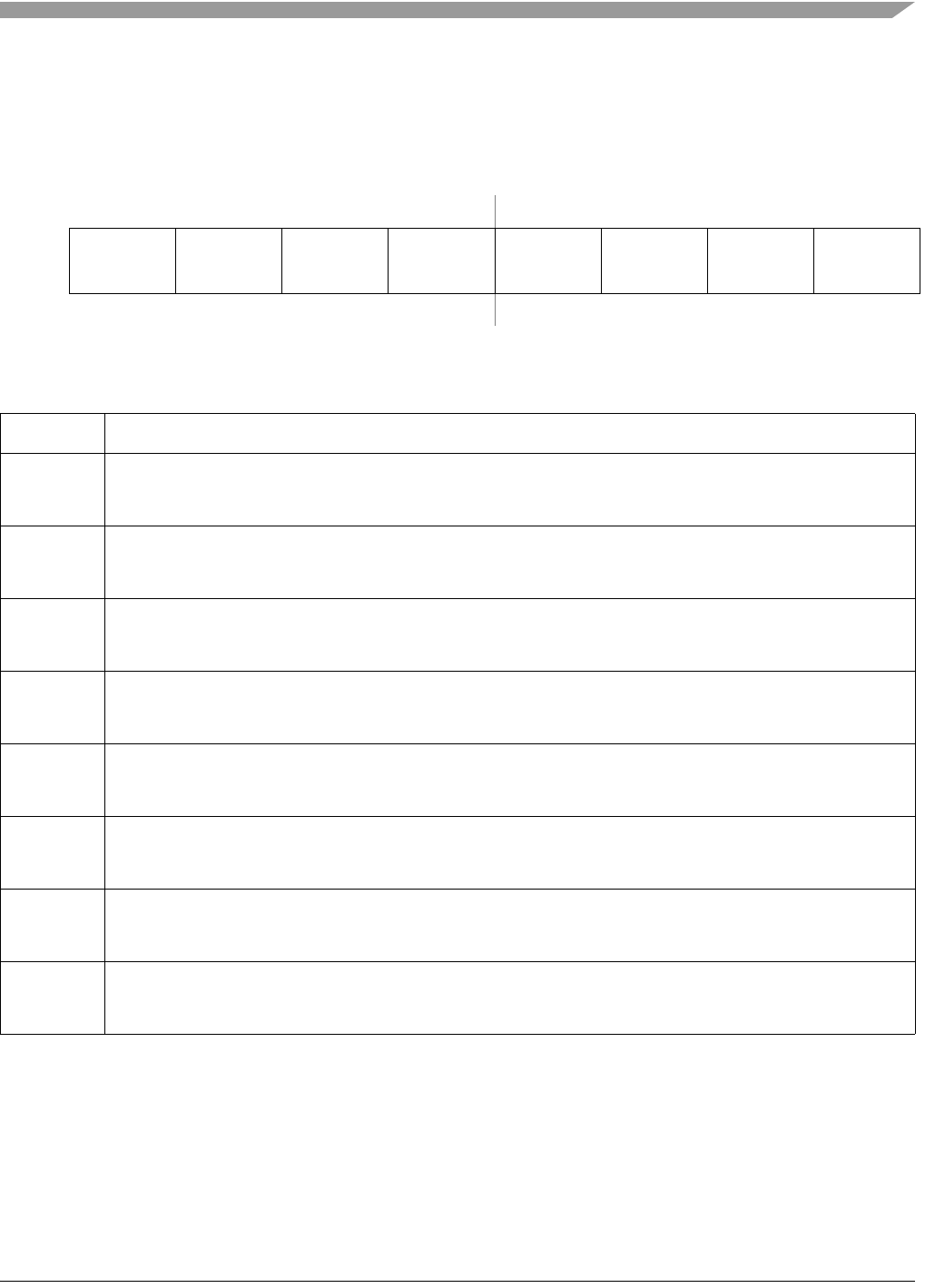

76543210

R

TPM3 TPM2 TPM1 ADC IIC2 IIC1 SCI2 SCI1

W

Reset:11111111

Figure 5-10. System Clock Gating Control 1 Register (SCGC1)

Table 5-12. SCGC1 Register Field Descriptions

Field Description

7

TPM3

TPM3 Clock Gate Control. This bit controls the clock gate to the TPM3 module.

0 Bus clock to the TPM3 module is disabled.

1 Bus clock to the TPM3 module is enabled.

6

TPM2

TPM2 Clock Gate Control. This bit controls the clock gate to the TPM2 module.

0 Bus clock to the TPM2 module is disabled.

1 Bus clock to the TPM2 module is enabled.

5

TPM1

TPM1 Clock Gate Control. This bit controls the clock gate to the TPM1 module.

0 Bus clock to the TPM1 module is disabled.

1 Bus clock to the TPM1 module is enabled.

4

ADC

ADC Clock Gate Control. This bit controls the clock gate to the ADC module.

0 Bus clock to the ADC module is disabled.

1 Bus clock to the ADC module is enabled.

3

IIC2

IIC2 Clock Gate Control. This bit controls the clock gate to the IIC2 module.

0 Bus clock to the IIC2 module is disabled.

1 Bus clock to the IIC2 module is enabled.

2

IIC1

IIC1 Clock Gate Control. This bit controls the clock gate to the IIC1 module.

0 Bus clock to the IIC1 module is disabled.

1 Bus clock to the IIC1 module is enabled.

1

SCI2

SCI2 Clock Gate Control. This bit controls the clock gate to the SCI2 module.

0 Bus clock to the SCI2 module is disabled.

1 Bus clock to the SCI2 module is enabled.

0

SCI1

SCI1 Clock Gate Control. This bit controls the clock gate to the SCI1 module.

0 Bus clock to the SCI1 module is disabled.

1 Bus clock to the SCI1 module is enabled.