Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 365

Get the latest version from freescale.com

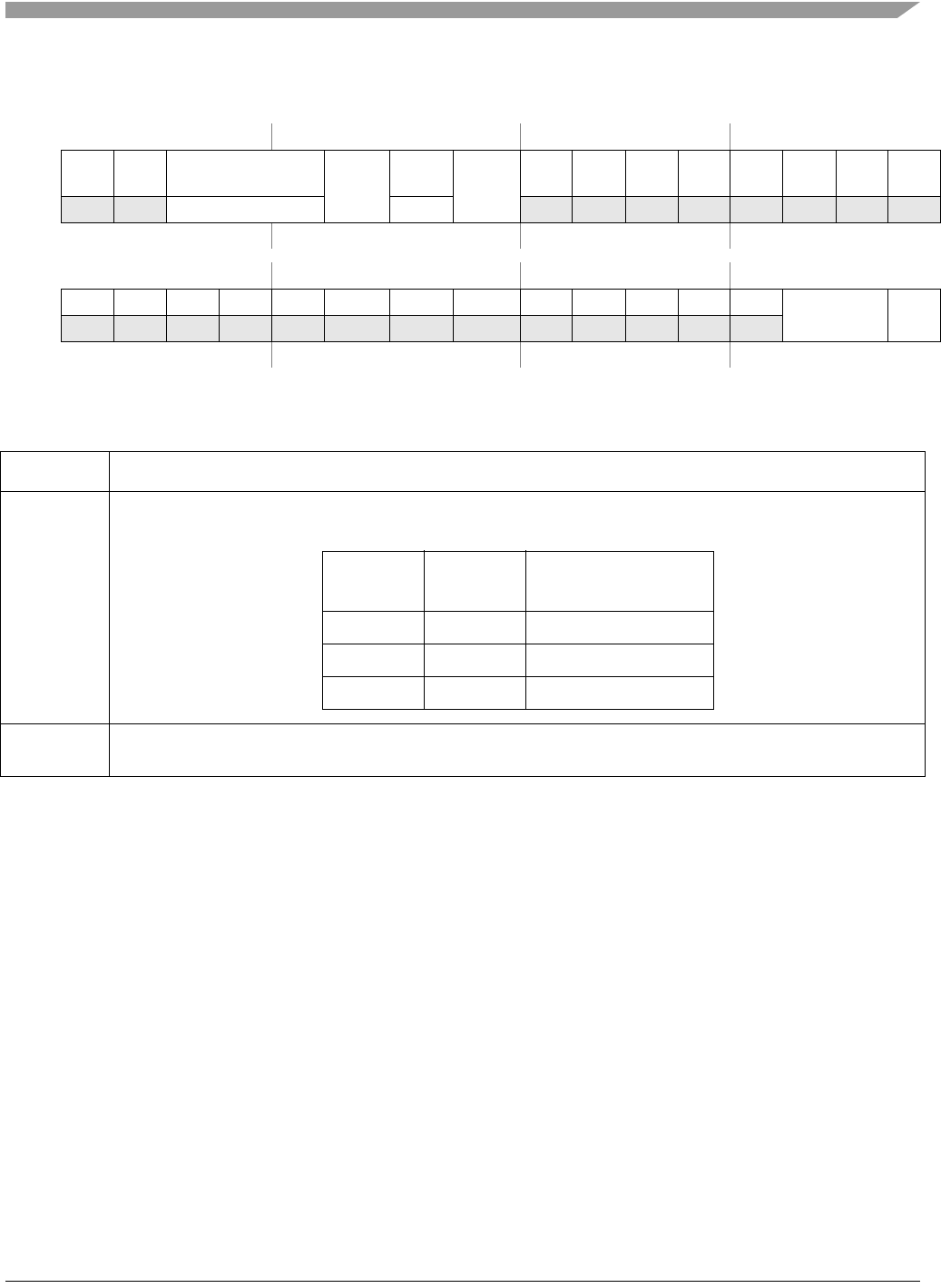

DRc: 0x01 (XCSR) Access: Supervisor write-only

BDM read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R CPU

HALT

CPU

STOP

CSTAT

CLKSW

SEC

ENBDM

0000

0 000

W ESEQC ERASE

Reset00000 0 0 0 00000000

151413121110 9 8 76543210

R 0 0000 0 0 0 00 0 0 0

APCSC

APCE

NB

W

Reset00000 0 0 0 00000000

Figure 18-4. Extended Configuration/Status Register (XCSR)

Table 18-7. XCSR Field Descriptions

Field Description

31

CPUHALT

Indicates that the CPU is in the halt state. The CPU state may be running, stopped, or halted, which is determined

by the CPUHALT and CPUSTOP bits as shown below.

30

CPUSTOP

Indicates that the CPU is in the stop state. The CPU state may be running, stopped, or halted, which is determined

by the CPUHALT and CPUSTOP bits as shown in the CPUHALT bit description.

XCSR

[CPUHALT]

XCSR

[CPUSTOP]

CPU State

0 0 Running

0 1 Stopped

10Halted