MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 45

Get the latest version from freescale.com

Chapter 3 Modes of Operation

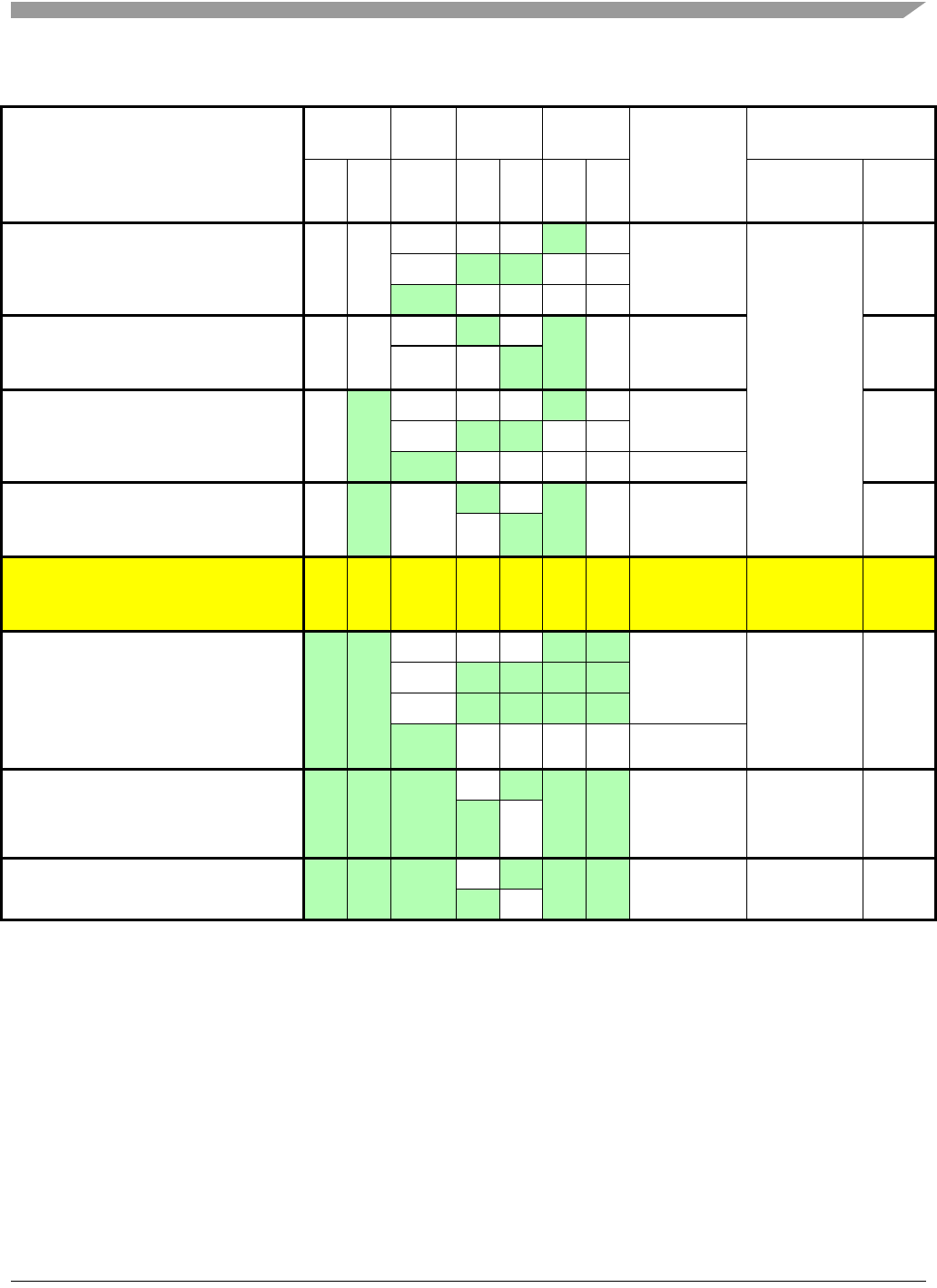

Table 3-1. CPU / Power Mode Selections

Mode of Operation

SOPT1

SIM

CSR2

BDC

SPMSC1

PMC

SPMSC2

PMC

CPU and

Peripheral Clocks

Effects on Sub-System

STOPE

WAITE

ENBDM

1

1

ENBDM is located in the upper byte of the XCSR register which is write-accessible only through BDC commands, see

Section 18.3.2, “Extended Configuration/Status Register (XCSR)”.

LVDE

LVDSE

LPR

PPDC

BDC Clock

Switched

Power

Run mode - processor and peripherals clocked

normally.

xx

xxx

0x

On. ICS in any

mode

On

Note: When not

needed, the BDC

clock can be gated

off at the discretion

of the processor.

The clock is

available within a

few cycles of

demand by the

processor,

normally when a

negative edge is

detected on

BKGD. The BDM

command

associated with

that negative edge

may not take

affect.

Onx

1 1xx

1 xxxx

LPrun mode with low voltage detect disabled -

processor and peripherals clocked at low

frequency

2

.

Low voltage detects are not active.

2

250 kHz maximum CPU frequency in LPrun; 125 kHz maximum peripheral clock frequency.

xx

0

0x

10

Low freq required.

ICS in FBELP

mode.

Loose Reg

01

0

Wait mode - processor clock nominally inactive, but

peripherals are clocked.

x

1

xxx

0x

Periph clocks on.

CPU clock on if

ENBDM=1.

Onx

1 1xx

1 xxxx On

LPwait mode - processor clock is inactive,

peripherals are clocked at low frequency and the

PMC is loosely regulating.

Low voltage detects are not active.

x

10

0x

10

CPU clock is off.

Periph clocks at

low speed.

ICS in FBELP.

Loose Reg

1

0

Stop modes disabled; Illegal opcode reset if STOP

instruction executed and CPUCR[IRD] is cleared,

else illegal instruction exception is generated.

0 0

Function

of BKGD/

MS at

reset

⇒1 ⇒1 ⇒0 ⇒0 ⇒On

Function of

BKGD/MS at reset

⇒On

Stop4 - Either low-power modes have not been

requested, or low voltage detects are enabled or

ENBDM = 1.

1 0

xxx

0 0

Peripheral clocks

off. CPU clock on if

ENBDM=1.

BDC clock enabled

only if ENBDM=1

prior to entering

stop.

On

x

1 1 1 0

x

1 1 0 1

1 xxxx

CPU clock on.

Periph clocks off.

Stop3 - Low voltage detect in stop is not enabled.

Clocks must be at low frequency and are gated. The

regulator is in loose regulation.

1 0 0

1

0

1 0

Low freq required.

ICS in FBELP

mode. CPU and

peripheral clocks

are gated off.

Off Loose Reg

0x

Stop2 - Low voltage detects are not active. If BDC is

enabled, stop4 is invoked rather than stop2.

1 0

1 0

0 1N/A N/A Off

0x