MCF51QE128 MCU Series Reference Manual, Rev. 3

Freescale Semiconductor 103

Get the latest version from freescale.com

Chapter 5 Resets, Interrupts, and General System Control

5.7.6 System Power Management Status and Control 1 Register

(SPMSC1)

This high page register contains status and control bits to support the low voltage detect function, and it

enables the bandgap voltage reference for use by the ADC module. To configure the low voltage detect

trip voltage, see Table 5-10 for the LVDV bit description in SPMSC3.

SPMSC1 is not reset when exiting from stop2.

76543210

R ID[11:8]

W

Reset:———— 1 1 0 0

Figure 5-5. System Device Identification Register High (SDIDH)

Table 5-6. SDIDH Register Field Descriptions

Field Description

7–4

Reserved

Reserved. Reading these bits results in an indeterminate value; writes have no effect.

3–0

ID[11:8]

Part Identification Number. Each derivative in the ColdFire family has a unique identification number. The

MCF51QE128/64/32 are hard coded to the value 0xC15. See also ID bits in Ta bl e 5- 7 .

76543210

R ID[7:0]

W

Reset:00010101

Figure 5-6. System Device Identification Register Low (SDIDL)

Table 5-7. SDIDL Register Field Descriptions

Field Description

7–0

ID[7:0]

Part Identification Number. Each derivative in the ColdFire family has a unique identification number. The

MCF51QE128/64/32 are hard coded to the value 0xC15. See also ID bits in Ta bl e 5- 6 .

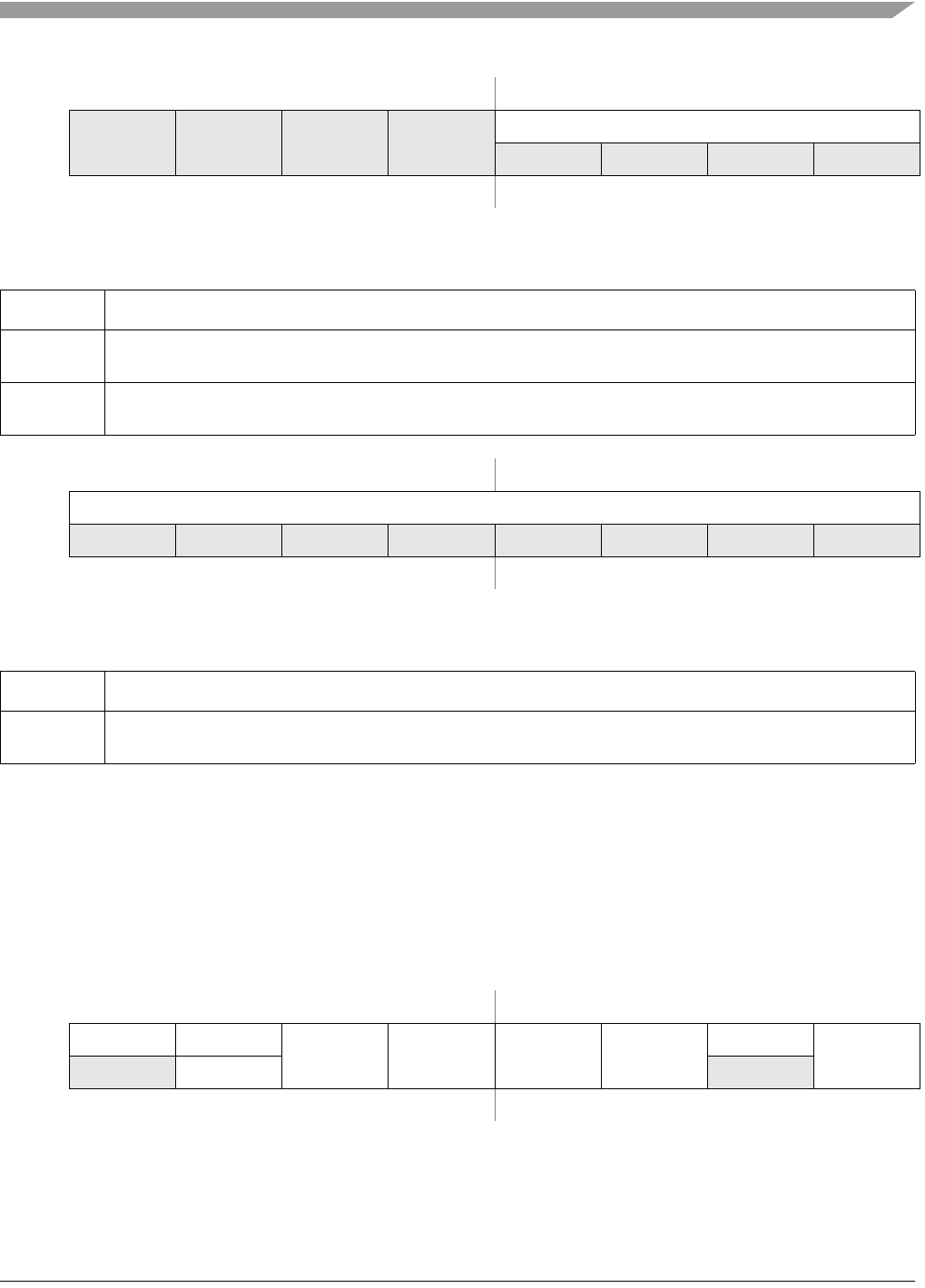

76543210

RLVDF 0

LVDIE LVDRE

2

LVDSE LVDE

2

0

1

BGBE

W LVDACK

Reset:00011100

1

Bit 1 is a reserved bit that must always be written to 0.

2

This bit can be written only one time after reset. Additional writes are ignored.

Figure 5-7. System Power Management Status and Control 1 Register (SPMSC1)