ColdFire Core

MCF51QE128 MCU Series Reference Manual, Rev. 3

172 Freescale Semiconductor

7.3.4.6 Branch Instruction Execution Times

TPF.W 1(0/0)———— — ——

TPF.L 1(0/0)———— — ——

UNLK Ax 2(1/0) — — — — — — —

WDDATA <ea> — 3(1/0) 3(1/0) 3(1/0) 3(1/0) 4(1/0) 3(1/0) —

WDEBUG<ea> —5(2/0)— —5(2/0) — — —

1

The n is the number of registers moved by the MOVEM opcode.

2

If a MOVE.W #imm,SR instruction is executed and imm[13] equals 1, the execution time is 1(0/0).

3

The execution time for STOP is the time required until the processor begins sampling continuously for interrupts.

4

PEA execution times are the same for (d16,PC).

5

PEA execution times are the same for (d8,PC,Xn*SF).

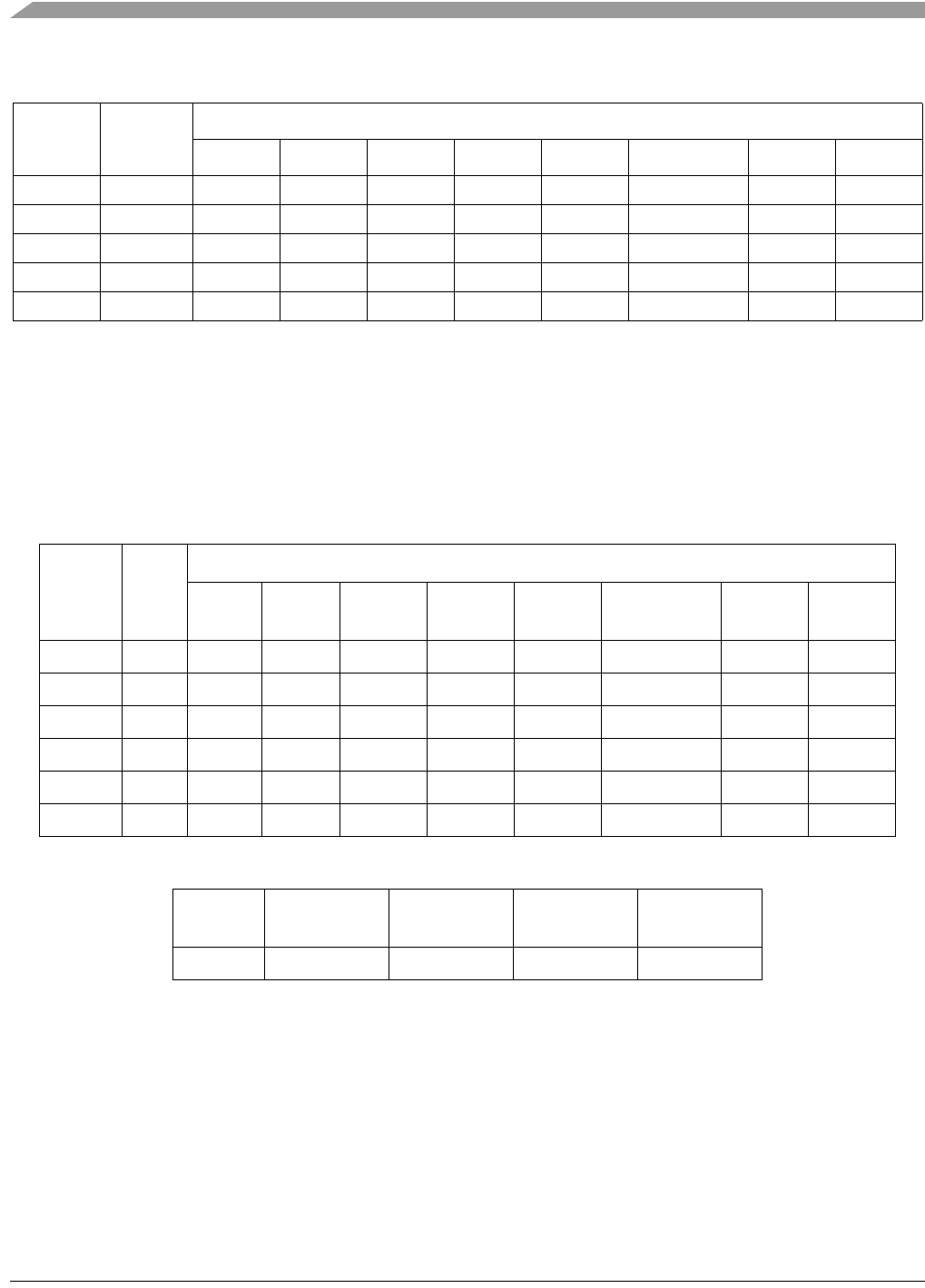

Table 7-19. General Branch Instruction Execution Times

Opcode <EA>

Effective Address

Rn (An) (An)+ -(An)

(d16,An)

(d16,PC)

(d8,An,Xi*SF)

(d8,PC,Xi*SF)

xxx.wl #xxx

BRA — — — — 2(0/1) — — —

BSR — — — — 3(0/1) — — —

JMP <ea> — 3(0/0) — — 3(0/0) 4(0/0) 3(0/0) —

JSR <ea> — 3(0/1) — — 3(0/1) 4(0/1) 3(0/1) —

RTE — — 10(2/0) — — — — —

RTS ——5(1/0)—————

Table 7-20. Bcc Instruction Execution Times

Opcode

Forward

Taken

Forward

Not Taken

Backward

Taken

Backward

Not Taken

Bcc 3(0/0) 1(0/0) 2(0/0) 3(0/0)

Table 7-18. Miscellaneous Instruction Execution Times (continued)

Opcode <EA>

Effective Address

Rn (An) (An)+ -(An) (d16,An) (d8,An,Xn*SF) xxx.wl #xxx