Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

402 Freescale Semiconductor

Get the latest version from freescale.com

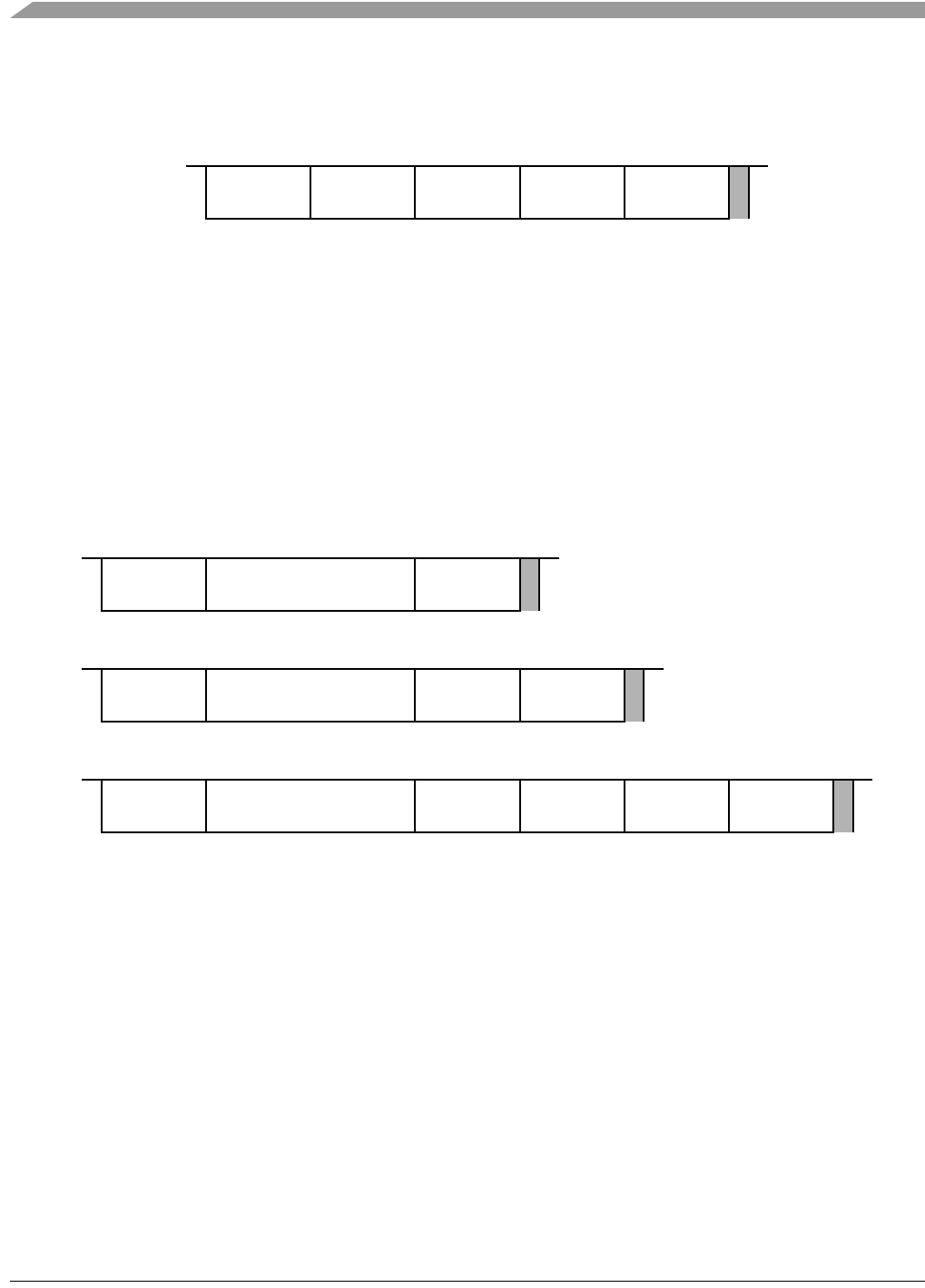

18.4.1.5.19 WRITE_DREG

This command writes the 32-bit operand to the selected debug control register. This grouping includes all

the debug control registers ({X}CSRn, BAAR, AATR, TDR, PBRn, PBMR, ABxR, DBR, DBMR).

Accesses to debug control registers are always 32-bits wide, regardless of implemented register width. The

register is addressed through the core register number (CRN). See Table 18-4 for CRN details.

18.4.1.5.20 WRITE_MEM.sz, WRITE_MEM.sz_WS

Write debug control register Non-intrusive

0x80+CRN

DREG data

[31–24]

DREG data

[23–16]

DREG data

[15–8]

DREG data

[7–0]

host →

target

host →

target

host →

target

host →

target

host →

target

D

L

Y

WRITE_MEM.sz

Write memory at the specified address Non-intrusive

0x10 Address[23-0]

Memory

data[7–0]

host →

target

host → target

host →

target

D

L

Y

0x14 Address[23-0]

Memory

data[15–8]

Memory

data[7–0]

host →

target

host → target

host →

target

host →

target

D

L

Y

0x18 Address[23-0]

Memory

data[31–24]

Memory

data[23–16]

Memory

data[15–8]

Memory

data[7–0]

host →

target

host → target

host →

target

host →

target

host →

target

host →

target

D

L

Y