MCF51QE128 MCU Series Reference Manual, Rev. 3

100 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 5 Resets, Interrupts, and General System Control

5.7.3 System Options Register 1 (SOPT1)

All SOPT1 bit fields, except WAITE, are write-once. Therefore for the write-once bits, only the first write

after reset is honored. Any subsequent attempt to write to these bit fields (intentionally or unintentionally)

is ignored to avoid accidental changes to these sensitive settings. All bit fields may be read at any time and

WAITE is write-anytime. SOPT1 should be written during the reset initialization program to set the desired

controls even if the desired settings are the same as the reset settings.

4

ILOP

Illegal Opcode. Reset was caused by an attempt to execute an unimplemented or illegal opcode. This includes

any illegal instruction (except the ILLEGAL (0x4AFC) opcode) or a privilege violation (execution of a supervisor

instruction in user mode. The STOP instruction is considered illegal if SOPT1[STOPE,WAITE] are cleared. The

HALT instruction is considered illegal if the BDM interface is disabled (XCSR[ENBDM] = 0).

All illegal opcode resets are enabled when CPUCR[IRD] is cleared. If CPUCR[IRD] is set, then the appropriate

processor exception is generated instead of a reset.

0 Reset not caused by an illegal opcode.

1 Reset caused by an illegal opcode.

3

ILAD

Illegal Address. Reset was caused by the processor's attempted access of an illegal address in the memory map,

an address error, an RTE format error, or a fault-on-fault condition. All the illegal address resets are enabled when

CPUCR[ARD] is cleared. When CPUCR[ARD] is set, the appropriate processor exception is generated instead

of a reset, or if a fault-on-fault condition is reached, the processor simply halts.

0 Reset not caused by an illegal access.

1 Reset caused by an illegal access.

2 Reserved, should be cleared.

1

LVD

Low Voltage Detect. If LVDRE is set and the supply drops below the LVD trip voltage, an LVD reset occurs. This

bit is also set by POR.

0 Reset not caused by LVD trip or POR.

1 Reset caused by LVD trip or POR.

0 Reserved, should be cleared.

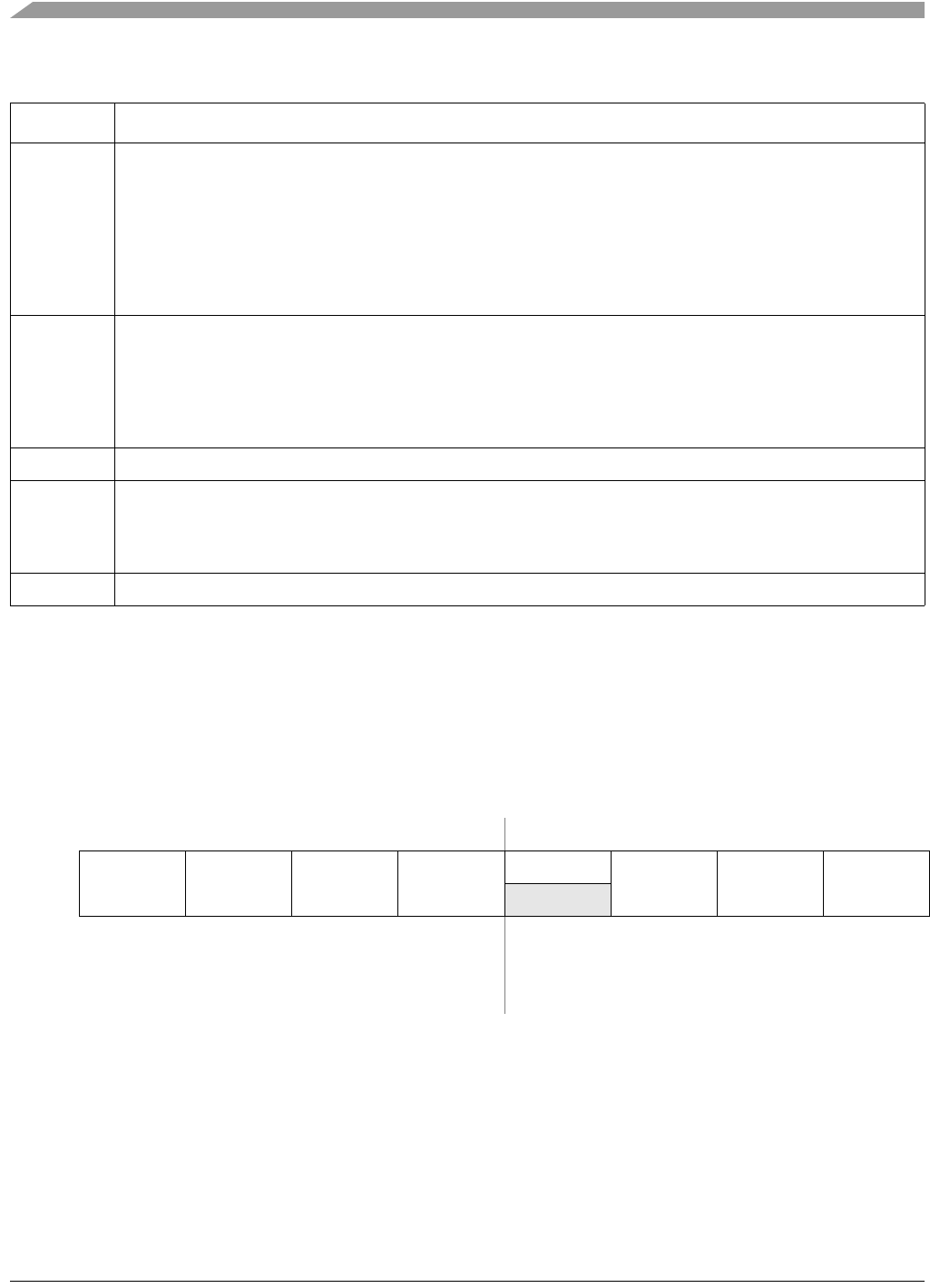

76543210

R

COPE COPT STOPE WAITE

0

RSTOPE BKGDPE RSTPE

W

Reset:11010u

1

1u

1

POR:11010010

LVR:11010010

1

u = unaffected

Figure 5-3. System Options Register 1 (SOPT1)

Table 5-3. SRS Register Field Descriptions (continued)

Field Description