Chapter 18 Version 1 ColdFire Debug (CF1_DEBUG)

MCF51QE128 MCU Series Reference Manual, Rev. 3

406 Freescale Semiconductor

Get the latest version from freescale.com

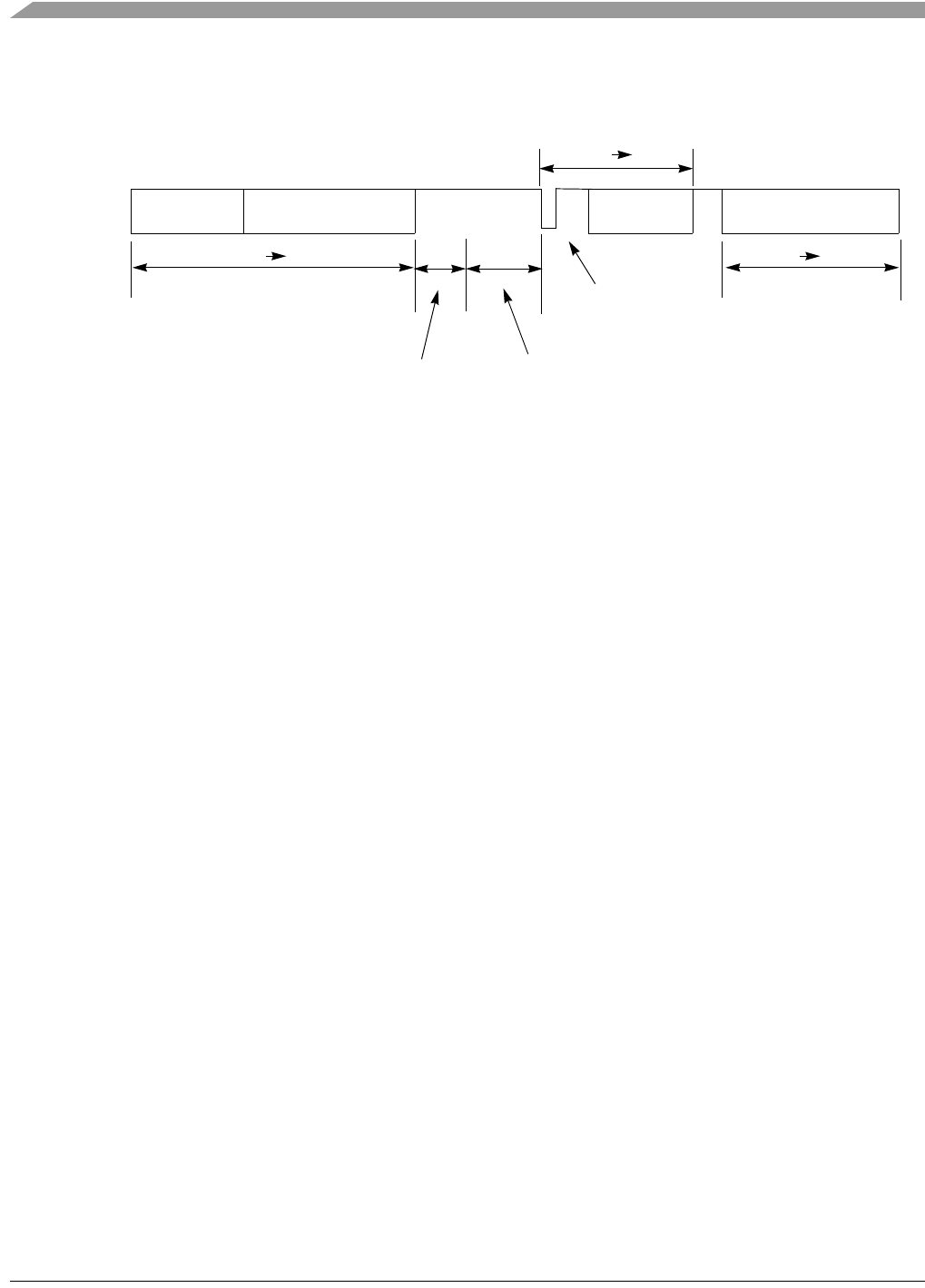

indicating that the addressed byte is ready to be retrieved. After detecting the ACK pulse, the host initiates

the data-read portion of the command.

Figure 18-20. Handshake Protocol at Command Level

Unlike a normal bit transfer, where the host initiates the transmission by issuing a negative edge in the

BKGD pin, the serial interface ACK handshake pulse is initiated by the target MCU. The hardware

handshake protocol in Figure 18-20 specifies the timing when the BKGD pin is being driven, so the host

should follow these timing constraints in order to avoid the risks of an electrical conflict at the BKGD pin.

The ACK handshake protocol does not support nested ACK pulses. If a BDC command is not

acknowledged by an ACK pulse, the host first needs to abort the pending command before issuing a new

BDC command. When the CPU enters a stop mode at about the same time the host issues a command that

requires CPU execution, the target discards the incoming command. Therefore, the command is not

acknowledged by the target, meaning that the ACK pulse is not issued in this case. After a certain time,

the host could decide to abort the ACK protocol in order allow a new command. Therefore, the protocol

provides a mechanism where a command (a pending ACK) could be aborted. Unlike a regular BDC

command, the ACK pulse does not provide a timeout. In the case of a STOP instruction where the ACK

is prevented from being issued, it would remain pending indefinitely if not aborted. See the handshake

abort procedure described in Section 18.4.1.7, “Hardware Handshake Abort Procedure.”

18.4.1.7 Hardware Handshake Abort Procedure

The abort procedure is based on the SYNC command. In order to abort a command that has not responded

with an ACK pulse, the host controller generates a sync request (by driving BKGD low for at least 128

serial clock cycles and then driving it high for one serial clock cycle as a speedup pulse). By detecting this

long low pulse on the BKGD pin, the target executes the sync protocol (see Section 18.4.1.5.1, “SYNC”),

and assumes that the pending command and therefore the related ACK pulse, are being aborted. Therefore,

after the sync protocol completes, the host is free to issue new BDC commands.

Note, since the host knows the target BDC clock frequency, the SYNC command does not need to consider

the lowest possible target frequency. In this case, the host could issue a SYNC very close to the 128 serial

clock cycles length, just providing a small overhead on the pulse length in order to assure the sync pulse

is not misinterpreted by the target.

It is important to notice that any issued BDC command that requires CPU execution is scheduled for

execution by the pipeline based on the dynamic state of the machine, provided the processor does not enter

READ_MEM.B

BDC ISSUES THE

BYTE IS

NEW BDC COMMAND

BKGD PIN

ADDRESS[23–0]

CPU EXECUTES THE

READ_MEM.B

COMMAND

RETRIEVED

HOST TARGET

HOST TARGE T

HOST TARGET

DEBUG DECODES

THE COMMAND

ACK PULSE (NOT TO SCALE)