MCF51QE128 MCU Series Reference Manual, Rev. 3

184 Freescale Semiconductor

Get the latest version from freescale.com

Chapter 8 Interrupt Controller (CF1_INTC)

8.3.2.6 INTC Software and Level-n IACK Registers (n = 1,2,3,...,7)

The eight read-only interrupt acknowledge (IACK) registers can be explicitly addressed via

memory-mapped accesses or implicitly addressed via a processor-generated interrupt acknowledge cycle

during exception processing when CPUCR[IAE] is set. In either case, the interrupt controller's actions are

very similar.

First, consider an IACK cycle to a specific level, a level-n IACK. When this type of IACK arrives in the

interrupt controller, the controller examines all currently-active level-n interrupt requests, determines the

highest priority within the level, and then responds with the unique vector number corresponding to that

specific interrupt source. The vector number is supplied as the data for the byte-sized IACK read cycle.

If there is no active interrupt source at the time of the level-n IACK, a special spurious interrupt vector

(vector number 24 (0x18)) is returned. It is the responsibility of the service routine to manage this error

situation.

This protocol implies the interrupting peripheral is not accessed during the acknowledge cycle because the

interrupt controller completely services the acknowledge. This means the interrupt source must be

explicitly disabled in the peripheral device by the interrupt service routine. This approach provides unique

vector capability for all interrupt requests, regardless of the complexity of the peripheral device.

Second, the interrupt controller also supports the concept of a software IACK. This is the ability to query

the interrupt controller near the end of an interrupt service routine (after the current interrupt request has

been negated) to determine if there are any pending (but currently masked) interrupt requests. If the

response to the software IACK's byte operand read is non-zero, the service routine uses the returned value

as the vector number of the highest pending interrupt request and passes control to the appropriate new

handler. If the returned value is zero, there is no pending interrupt request.

This process avoids the overhead of a context restore and RTE instruction execution, followed

immediately by another interrupt exception and context save. In system environments with high rates of

interrupt activity, this mechanism can noticeably improve overall performance. For additional details on

software IACKs, see Section 8.6.3, “More on Software IACKs.”

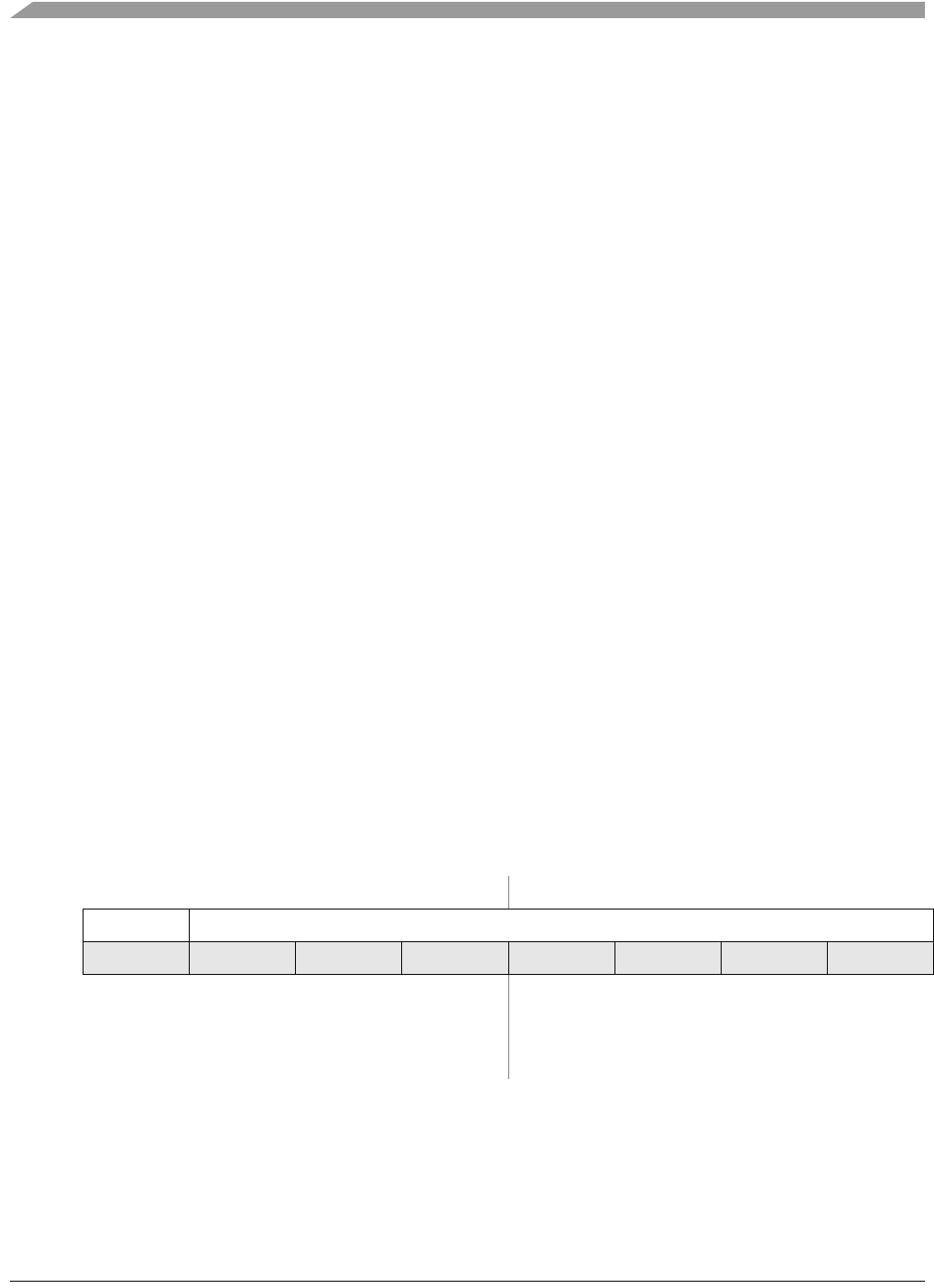

Figure 8-7. INTC_SWIACK, INTC_LVLnIACK Registers

Offset: CF1_INTC_BASE + 0x20 (INTC_SWIACK)

CF1_INTC_BASE + 0x20 + (4×n) (INTC_LVLnIACK)

Access: Read-only

76543210

R 0 VECN

W

SWIACK

Reset

00000000

LVLnIACK

Reset

00011000